Configuring clock monitoring, Clock monitoring module overview, Reference source level – H3C Technologies H3C SR8800 User Manual

Page 95: Priority of the reference source

83

Configuring Clock monitoring

Clock monitoring module overview

Clock monitoring module provides highly-precise, highly-reliable synchronous digital hierarchy (SDH)

line interface 38.88 MHz clock signals for different line processing units (LPUs). It implements such

functions as input clock source automatic selection, software phase-lock, and real-time monitoring of the

clock status of the interface card. The clock monitoring module supports hardware reset of the clock card.

The clock monitoring module supports 14 reference clock sources (referred to as reference source

hereinafter), among which the first and the second are Bits clock sources and the others are line clock

sources. The first and the second reference sources respectively correspond to external interfaces 1 and

2 for receiving clock signals on the active switching and routing processing unit (SRPU).

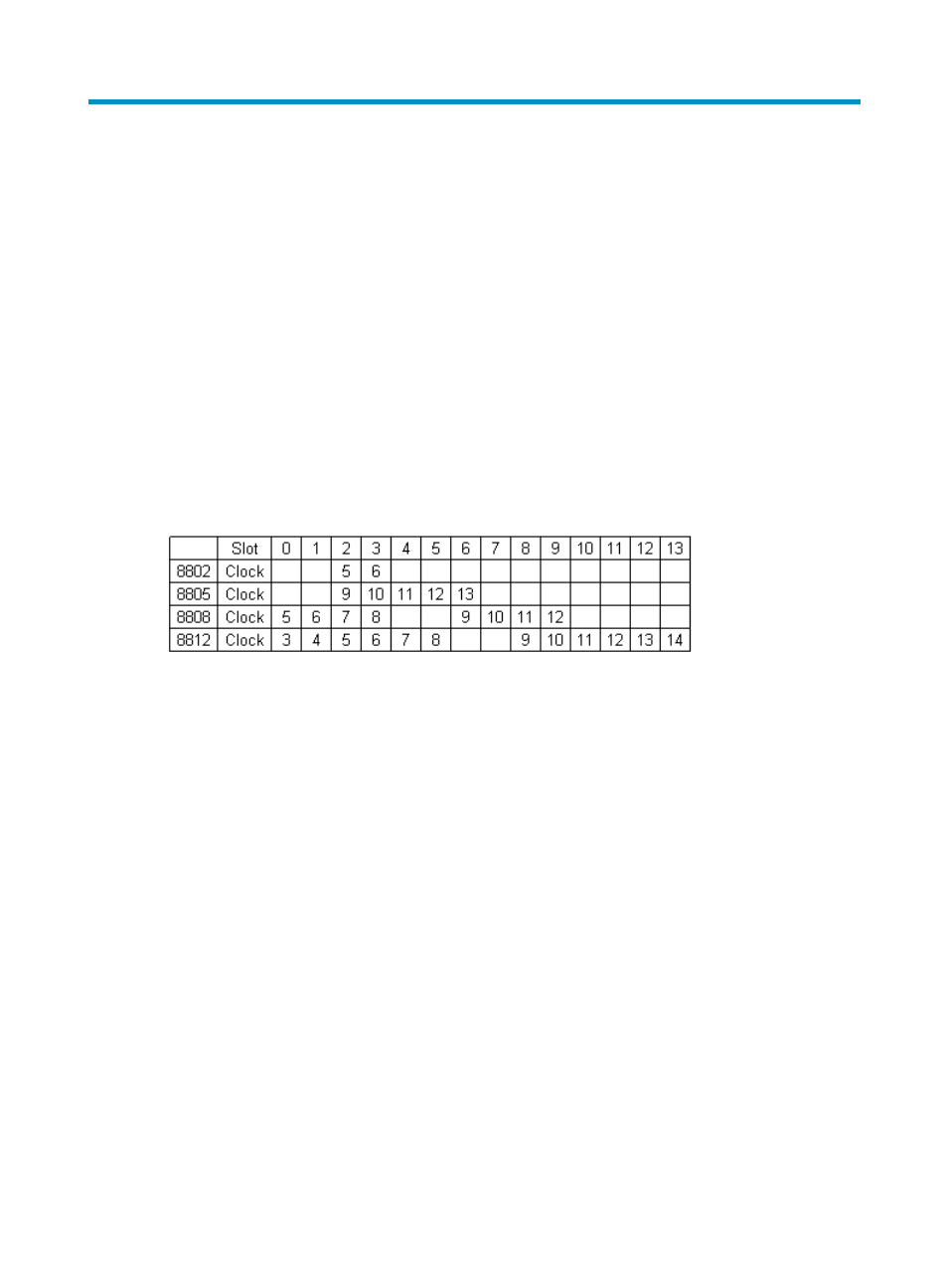

shows

the reference-slot relationship: On the SR8802, the clock in slot 2 corresponds to the fifth reference

source, and the clock in slot 3 corresponds to the sixth reference source.

Figure 32 Relationship between reference source and slot

Classification of clock sources

Clock sources can be classified into three categories according to different sources of the clock source:

•

Local clock source—38.88 MHz clock signals generated by a crystal oscillator inside the clock

monitoring module.

•

Bits clock source—Clock signals generated by a specific Bits clock device. The signals are sent to

the clock monitoring module through a specific interface on the SRPU (switch and router processing

unit) and then sent to all cards by the clock monitoring module.

•

Line clock source—Provided by the upper level device, whose precision is lower than that of the Bits

clock source. The signals are derived from the specified WAN interface and sent to the clock

monitoring module, which then sends the signals to all cards.

Reference source level

The reference source level is determined by the priority and the synchronization status marker (SSM) level

of the reference source.

Priority of the reference source

You can set a high priority for the reference source with high-precision and high-reliability to make it be

first selected as the clock source.

- H3C SR6600-X H3C SR6600 H3C SecPath F5020 H3C SecPath F5040 H3C VMSG VFW1000 H3C WX3000E Series Wireless Switches H3C WX5500E Series Access Controllers H3C WX3500E Series Access Controllers H3C WX2500E Series Access Controllers H3C WX6000 Series Access Controllers H3C WX5000 Series Access Controllers H3C LSWM1WCM10 Access Controller Module H3C LSUM3WCMD0 Access Controller Module H3C LSUM1WCME0 Access Controller Module H3C LSWM1WCM20 Access Controller Module H3C LSQM1WCMB0 Access Controller Module H3C LSRM1WCM2A1 Access Controller Module H3C LSBM1WCM2A0 Access Controller Module