Control and status interface, Clocks, Control and status interface -51 – Altera 40-Gbps Ethernet MAC and PHY MegaCore Function User Manual

Page 98: Clocks -51

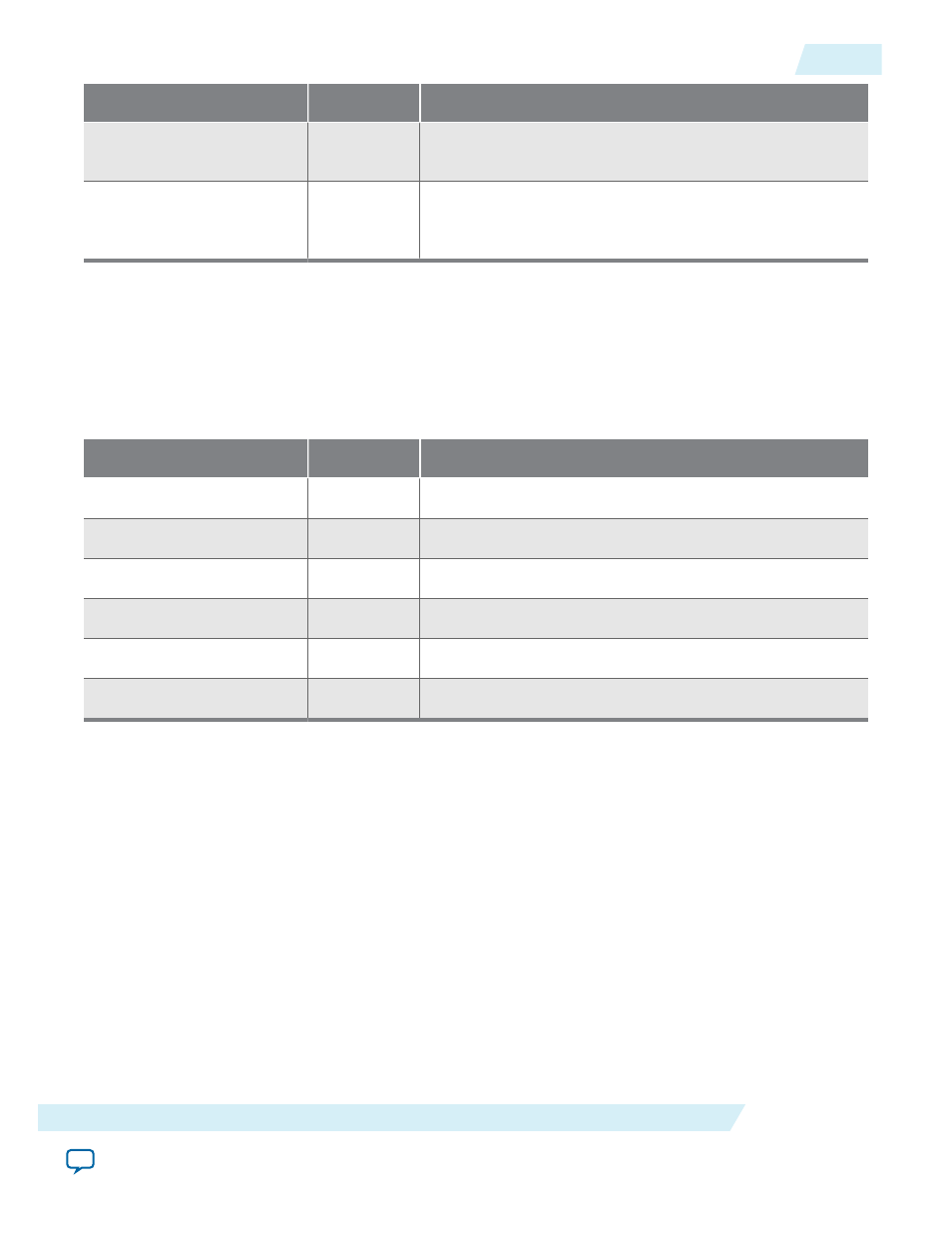

Signal Name

Direction

Description

upo_ber_max[3:0]

Output

When a bit is asserted, the BER counter for the

corresponding lane has rolled over.

upo_coef_max[3:0]

Output

When a bit is asserted, indicates that the remote coefficients

for the corresponding lane are at their maximum or

minimum values.

Control and Status Interface

The control and status interface provides an Avalon-MM interface to the control and status registers. The

Avalon-MM interface implements a standard memory-mapped protocol. You can connect an embedded

processor or JTAG Avalon master to this bus to access the control and status registers.

Table 3-15: Avalon-MM Control and Status Interface Signals

The

clk_status

clocks the signals on the 40-100GbE IP core control and status interface.

Signal Name

Direction

Description

status_addr

[15:0]

Input

Address for reads and writes

status_read

Input

Read command

status_write

Input

Write command

status_writedata

[31:0]

Input

Data to be written

status_readdata

[31:0]

Output

Read data

status_readdata_valid

Output

Read data is ready for use

The status interface is designed to operate at a low frequencies, typically 50 MHz for Stratix IV devices

and 100 MHz for Stratix V devices, so that control and status logic does not compete for resources with

the surrounding high speed datapath.

Related Information

•

•

on page 3-79

•

For more information about the Avalon-MM protocol, including timing diagrams, refer to the Avalon

Memory-Mapped Interfaces chapter.

Clocks

You must set the transceiver reference clock (

clk_ref

) frequency to a value that your IP core variation

supports. For most variations, The 40-100GbE IP core supports

clk_ref

frequencies of 644.53125 MHz

±100 ppm and 322.265625 MHz ± 100 ppm. The ±100ppm value is required for any clock source

providing the transceiver reference clock. For CAUI–4 variations, you must set the frequency of

clk_ref

UG-01088

2014.12.15

Control and Status Interface

3-51

Functional Description

Altera Corporation