Pause transmission logic, Pause control and generation interface, Pause control and generation interface -35 – Altera 40-Gbps Ethernet MAC and PHY MegaCore Function User Manual

Page 82

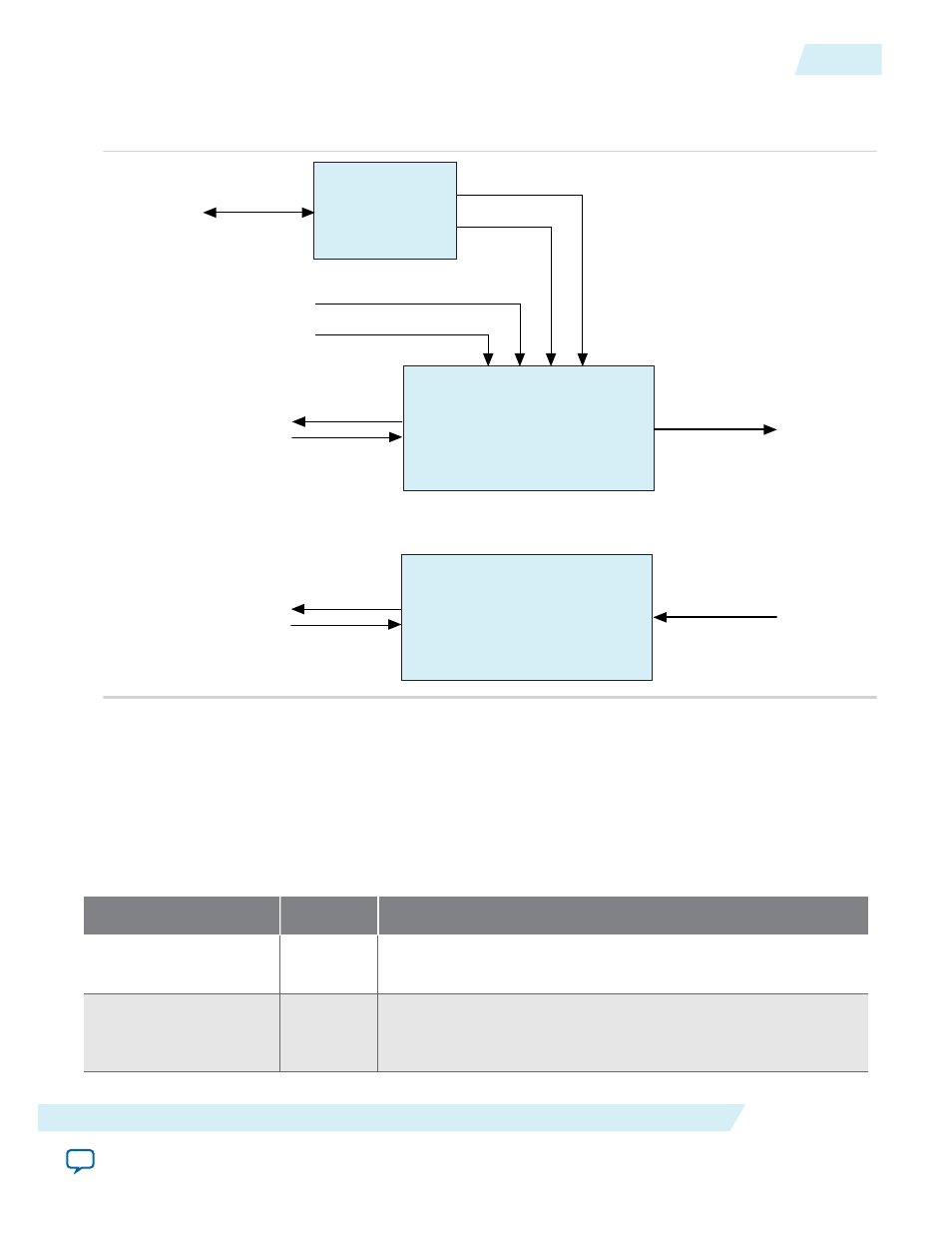

Pause Transmission Logic

Figure 3-29: Block Diagram of the Pause Transmission Logic

Tx MAC

Mac Data and Control

Frame Generator

Rx MAC

Frame Processor

XOFF_Gen

XON_Gen

XOFF_request (client)

XON_request (client)

Client MAC Tx

Interface

Client MAC Rx

Interface

XGMII Interface

Configuration

Registers

Avalon-MM Host

Interface

Pause Control and Generation Interface

The pause control interface implements flow control as specified by the IEEE 802.3ba 2010 100G Ethernet

Standard.The pause logic, upon receiving a pause packet, temporarily stops packet transmission, and can

pass the pause packets through as normal traffic or drop the pause control frames in the RX direction.

Table 3-7: Pause Control and Generation Signals

Describes the signals that implement pause control. You can also access the pause functionality using the pause

registers for any variant of the 40-100GbE IP core.

Signal Name

Direction

Description

pause_insert_tx

Input

Edge triggered signal which directs the IP core to insert a pause

frame on the Ethernet link.

pause_insert_time

[15:0]

Input

Specifies the duration of the pause in pause quanta. The pause

control settings in the pause registers determine the duration of

the pause quanta (pause quanta is equal to 512-bit time).

UG-01088

2014.12.15

Pause Transmission Logic

3-35

Functional Description

Altera Corporation