Mdio registers – Altera 40-Gbps Ethernet MAC and PHY MegaCore Function User Manual

Page 164

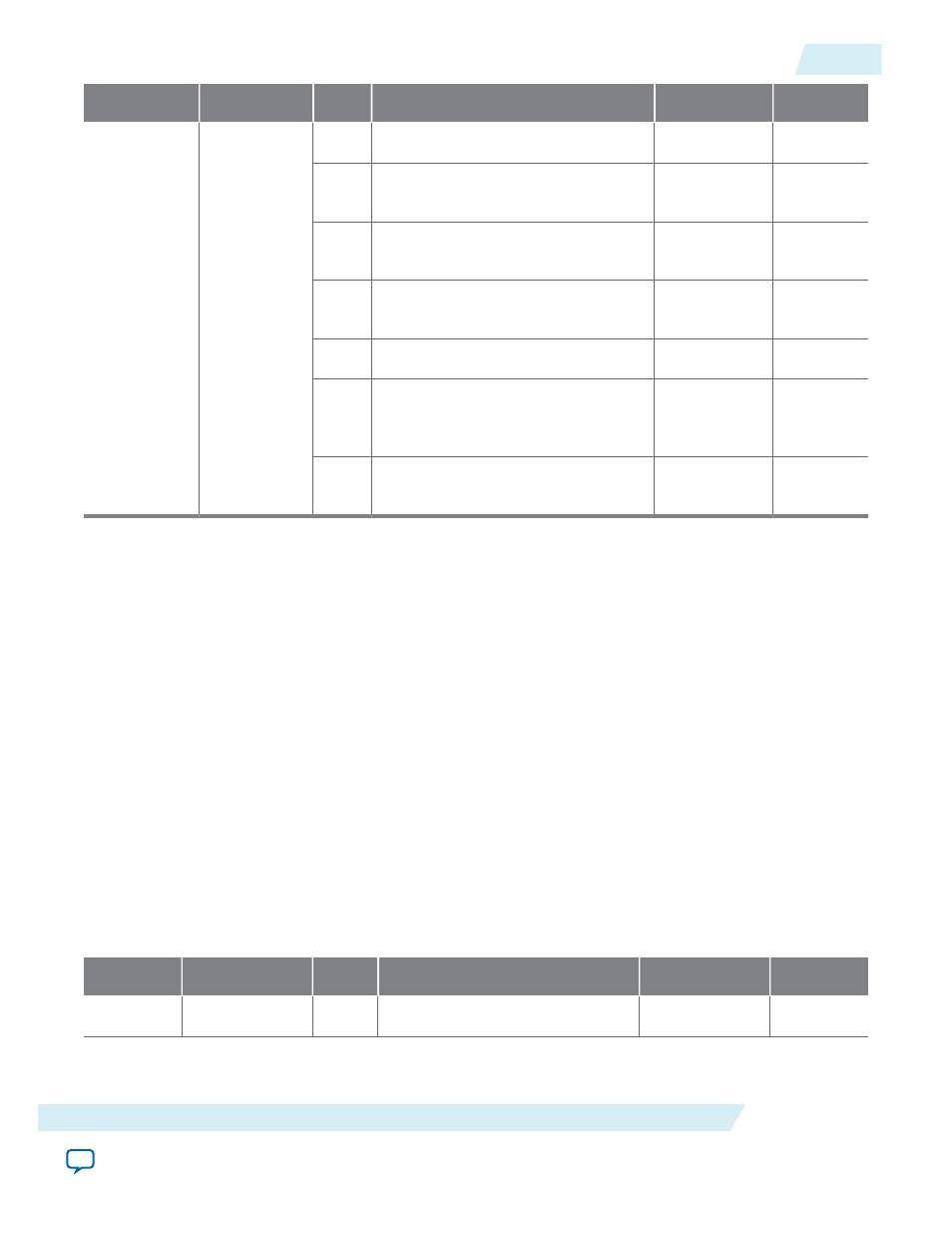

Address

Name

Bits

Description

HW Reset Value

Access

0x403

CMD_STATUS

[6]

PMD global alarm.

1b’0

R

[5]

Programmable alarm 3. Defaults to

module ready.

1b’0

R

[4]

Programmable alarm 2. Defaults to

high power mode on.

1b’0

R

[3]

Programmable alarm 1. Defaults to RX

CDR lock.

1b’0

R

[2]

RX side signal detected.

1’b0

R

[1]

When asserted, the PMD module is

physically plugged in. When

deasserted, it is offline.

1b’1

R

[0]

When 1, the PMD is resetting. When 0,

the PMD is available.

1’b1

R

Related Information

•

40-100GbE IP Core Example Design

Altera provides an example design with the 40-100GbE IP core. This example design is ready for

compilation and can be configured on a target device. The listed registers are part of the example

design.

•

For more information about PMD devices, refer to the Next Gen PMD CFP MSA Baseline Specifica‐

tions available on the CFP Multi-Source Agreement website.

MDIO Registers

The management data input/output (MDIO) interface is a serial bus interface for the Ethernet. In the

40-100GbE IP core example design, client logic drives the MDIO module when an MDIO serial interface

controls the external PMD or CFP device. This serial interface includes two wires, an MDC clock driven

by the MAC and a bidirectional data line which can be driven by up to 31 PHY slave devices. The

minimum clock frequency is 2.5 MHz. Refer to the specification of your PMD or CFP device for

additional information.

Table 3-51: MDIO Registers

Describes the MDIO registers in the 40-100GbE IP core example design. These registers are typically used to

communicate with an external optical module such as a PMD 100G optical module.

Address

Name

Bits

Description

HW Reset Value

Access

0x410

MDIO_WDATA

[15:0]

Data to be written.

0x0000

RW

UG-01088

2014.12.15

MDIO Registers

3-117

Functional Description

Altera Corporation