Altera 40-Gbps Ethernet MAC and PHY MegaCore Function User Manual

Page 118

The following 40-100GbE MAC and PHY IP core signals are not available in MAC-only IP core

variations:

• Clock signals:

•

clk_ref

(relevant only for IP core variations with the Sync–E support option turned off)

•

tx_clk_ref

(relevant only for IP core variations with the Sync-E support option turned on)

•

rx_clk_ref

(relevant only for IP core variations with the Sync-E support option turned on)

•

rx_recovered_clk

(relevant only for IP core variations with the Sync-E support option turned on)

• PCS and PMA reset signals:

•

pcs_tx_arst_ST

•

pcs_rx_arst_ST

•

pma_arst_ST

• Ethernet link signals

tx_serial

and

rx_serial

• PHY output status signals

tx_lanes_stable

and

lanes_deskewed

. Note that input signals with these

names are available, and should be supplied by the user logic that implements the PHY layer.

• Signals to connect to the external transceiver reconfiguration controller (relevant for Arria V GZ and

Stratix V devices only).

• 40GBASE-KR4 microprocessor interface and reconfiguration interface signals.

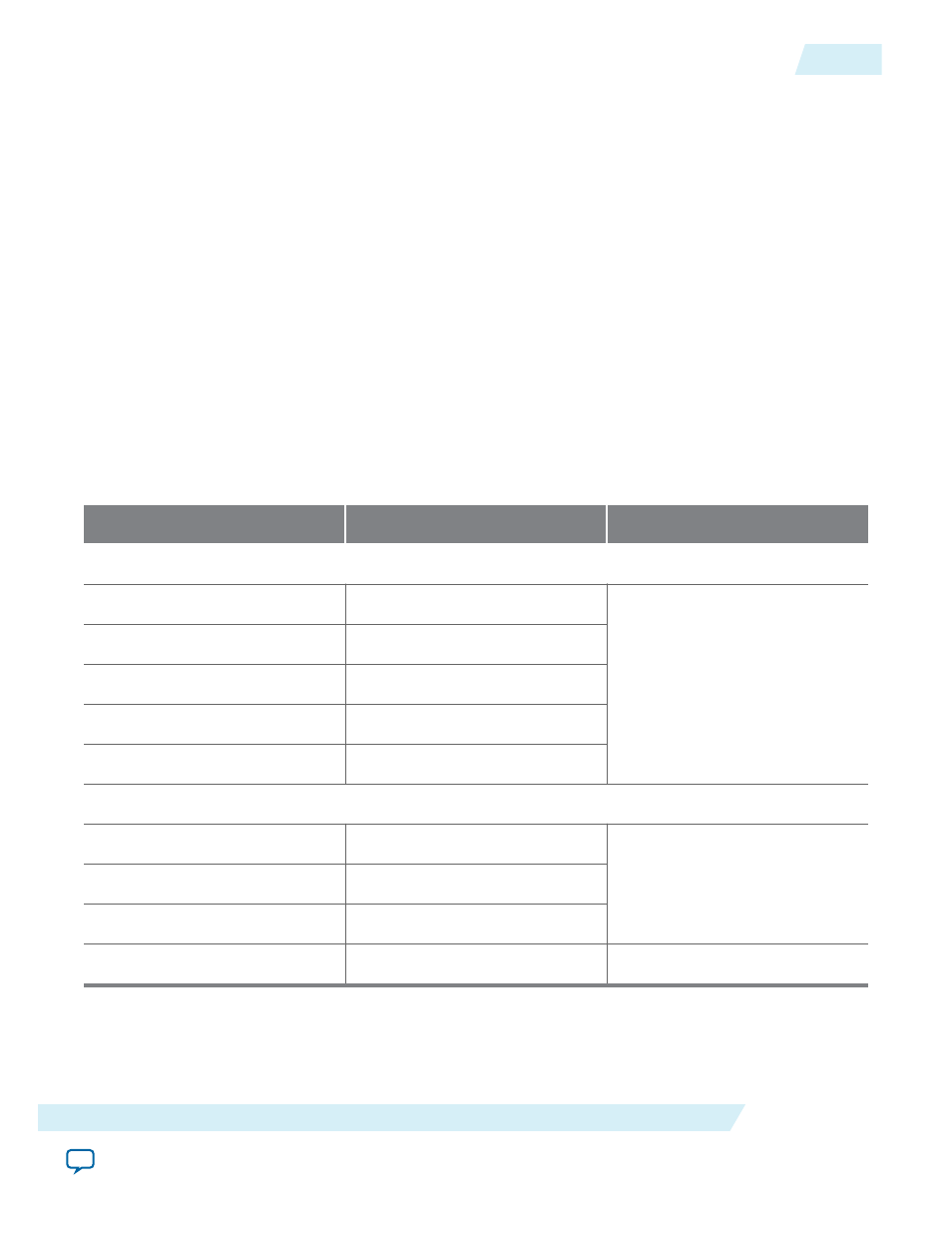

Table 3-21: 40-100GbE MAC IP Core Signals Not Visible in 40-100GbE MAC and PHY IP Core

Signal Name

Direction

Description

Transmit Side Signals

tx_mii_d[

Output

MAC to PHY connection

interface

tx_mii_c[

Output

tx_mii_valid

Output

tx_mii_ready

Input

tx_lanes_stable

Input

Receive Side Signals

rx_mii_d[

Input

PHY to MAC connection

interface

rx_mii_c[

Input

rx_mii_valid

Input

lanes_deskewed

Input

Lane to lane deskew interface

Note: When simulating the full design the

lanes

_

deskewed

input comes from the output of the RX PCS,

indicating a fully locked status. To avoid confusion, when simulating the

alt_e40_mac

or

alt_e100_mac

wrapper as the top level, drive the

lanes_deskewed

input and the

tx_mii_ready

input to '1'.

UG-01088

2014.12.15

Signals of 40-100GbE MAC‑Only IP Core Variations

3-71

Functional Description

Altera Corporation