Altera 40-Gbps Ethernet MAC and PHY MegaCore Function User Manual

Page 12

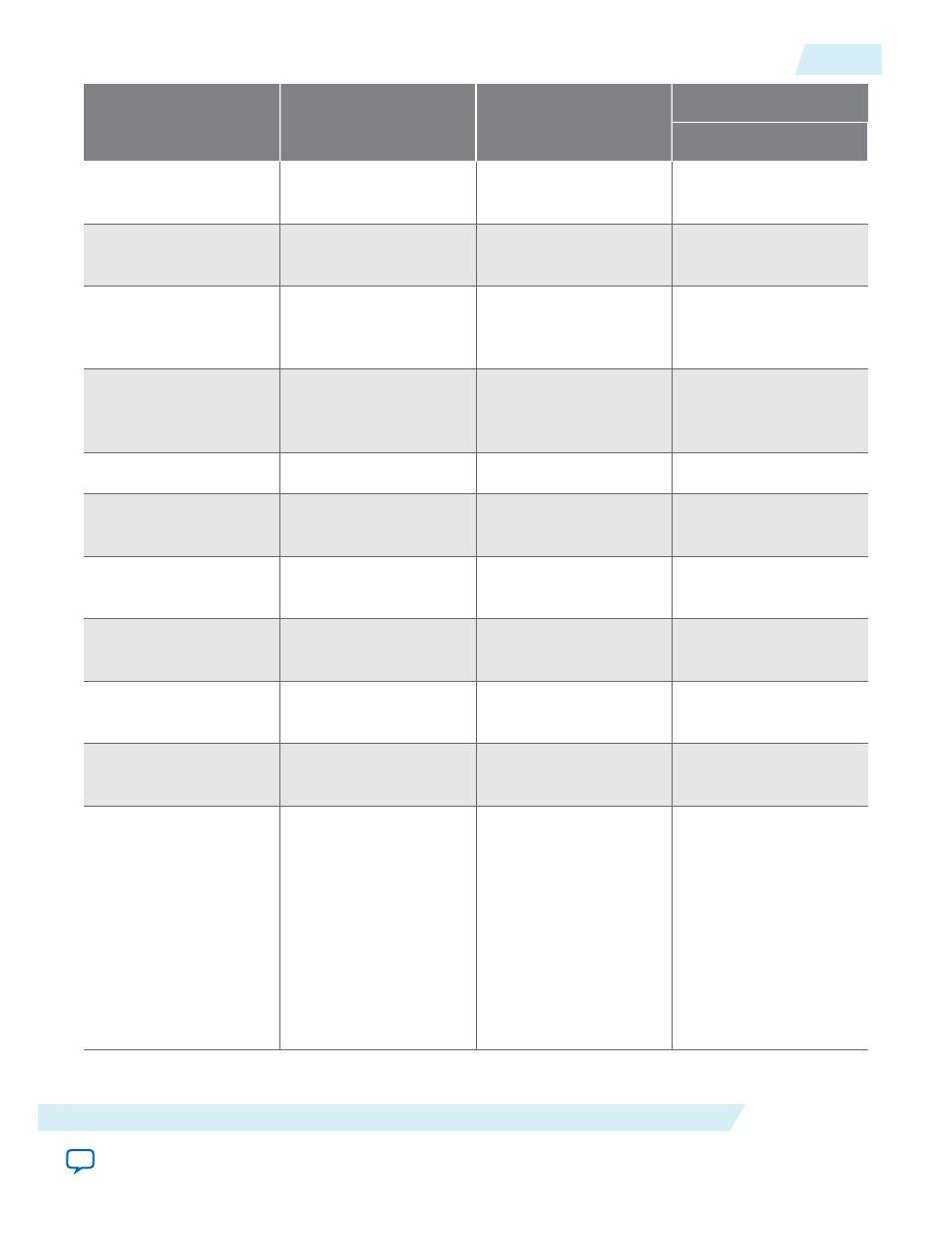

Module

ALMs

Logic Registers

Memory

M20K

• alt_e40_mac_

rx:mac_rx

3000

7000

9

• alt_e40_mac_

tx:mac_tx

2600

4800

0

• alt_e40_mac_

csr:mac_csr without

statistics counters

700

2000

0

• alt_e40_mac_

csr:mac_csr with

statistics counters

4600

8500

0

PHY

6800

8600

0

• alt_e40_phy_

pcs:phy_pcs

6200

8200

0

• • alt_e40_pcs_

rx:pcs_rx

2800

3800

0

• • alt_e40_pcs_

tx:pcs_tx

2900

3300

0

• • alt_e40_phy_

csr:phy_csr

500

1100

0

• alt_e40_phy_

pma:phy_pma

200

400

0

40GBASE-KR4 PHY

• No auto-negotiation

(AN)

• No link training

(LT)

• Forward error

correction (FEC)

only

• Use M20K blocks

for FEC buffer

14800

16700

8

UG-01088

2014.12.15

Resource Utilization for 40GbE IP Cores

1-9

About the 40- and 100-Gbps Ethernet MAC and PHY MegaCore Function

Altera Corporation

This manual is related to the following products: