100gbe ip core without adapters – Altera 40-Gbps Ethernet MAC and PHY MegaCore Function User Manual

Page 61

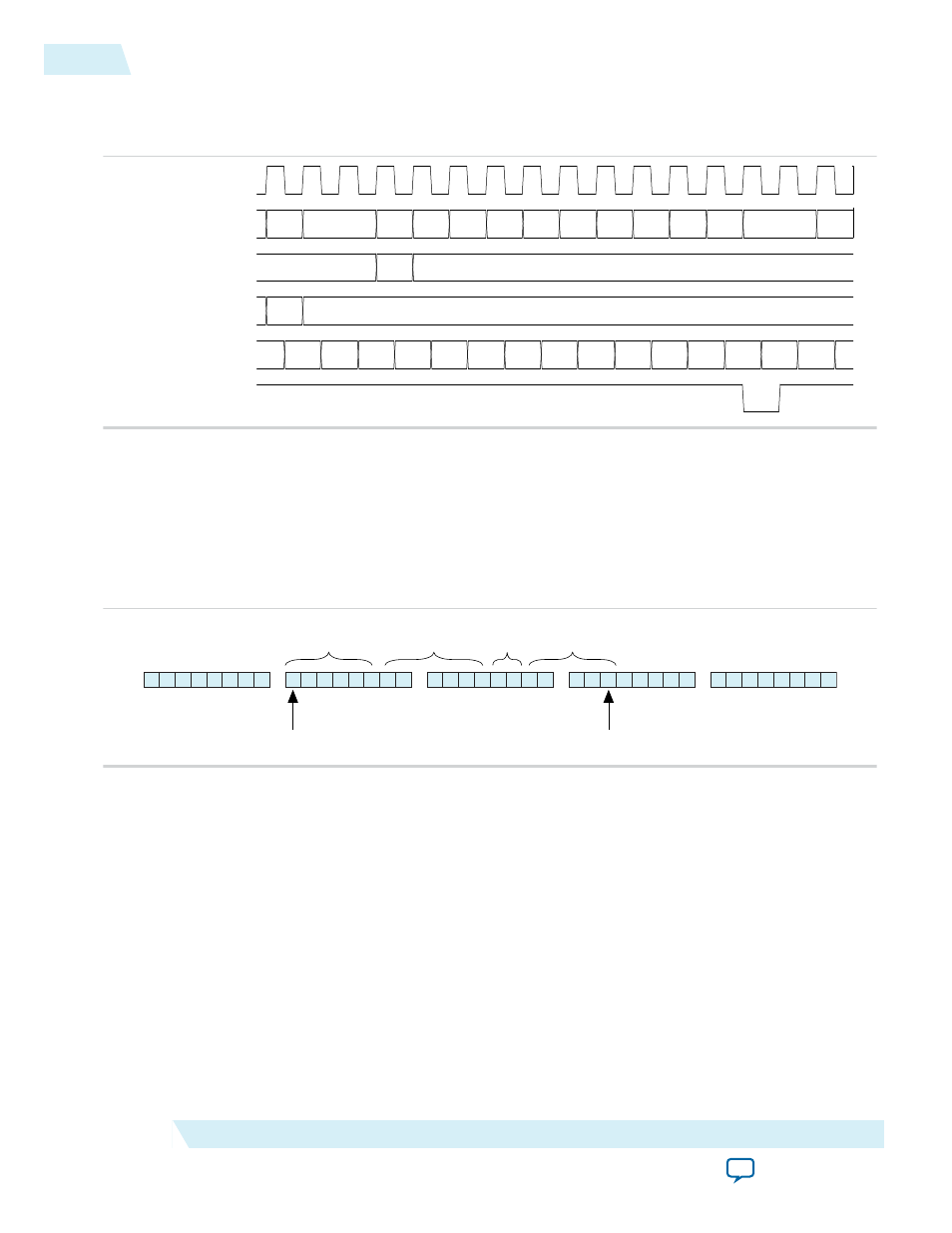

Figure 3-10: Sample 40GbE IP Core TX Bus Activity

Illustrates the deassertion of the

din_ack

signal. The data beginning with 0xe6e7 is not immediately

accepted. The

din

bus must be held until

din_ack

returns to one. At this point normal data flow resumes.

e40_tb.dut.clk_txmac

e40_tb.dut.din[127:0]

e40_tb.dut.din_start[1:0]

e40_tb.dut.din_end_pos[15:0]

e40_tb.dut.dout_d[127:0]

e40_tb.dut.din_ack

55565 .. 5555555555555 55555 .. 01010 .. 66676 .. 76777 .. 86878 .. 96979 .. A6A7A.. B6B7B .. C6C7C .. D6D7D.. E6E7E8E9EAEB .. F6F7F ..

1

0

0080

0000

13141.. 23242 .. 33343 .. 43444 .. 53545 .. 63646 .. 73747 .. 83848 .. 93949 .. A3A4A .. 02020 .. AEAFB .. BEBFC .. CECFD .. DEDFE .. 02020 .. E ..

100GbE IP Core Without Adapters

The following figures illustrate the transmission of a short packet when preamble pass-through is turned

off and when it is turned on.

Figure 3-11: Short Packet Example Without Preamble

Illustrates the transmission of a short packet for the 100GbE IP core when preamble pass-through is

turned off.

First data

Destination

MAC addr

Source

MAC Addr

Total

length

Last data

“hello”

Example 3-3: Bus Representation of a Short TX Packet Without Preamble

This example shows the Verilog HDL code that represents the simple packet illustrated in the

preceding figure. Note that bit

din_end[13]

corresponding to the “Last data” in the figure, is

asserted.

wire [6*8-1:0] dst_addr = 48’hffff ffff ffff;

wire [6*8-1:0] src_addr = 48’h0007 edff 1234;

wire [2*8-1:0] len = 16’d64;

din = {64’h0, dst_addr, src_addr, len, “hello”, 40’h0};

din_start = 5’b01000;

din_end = 40’b00000000_00000000_00000000_00100000_00000000;

3-14

100GbE IP Core Without Adapters

UG-01088

2014.12.15

Altera Corporation

Functional Description