40‑100gbe example design registers, Pmd registers, 100gbe example design registers -116 – Altera 40-Gbps Ethernet MAC and PHY MegaCore Function User Manual

Page 163

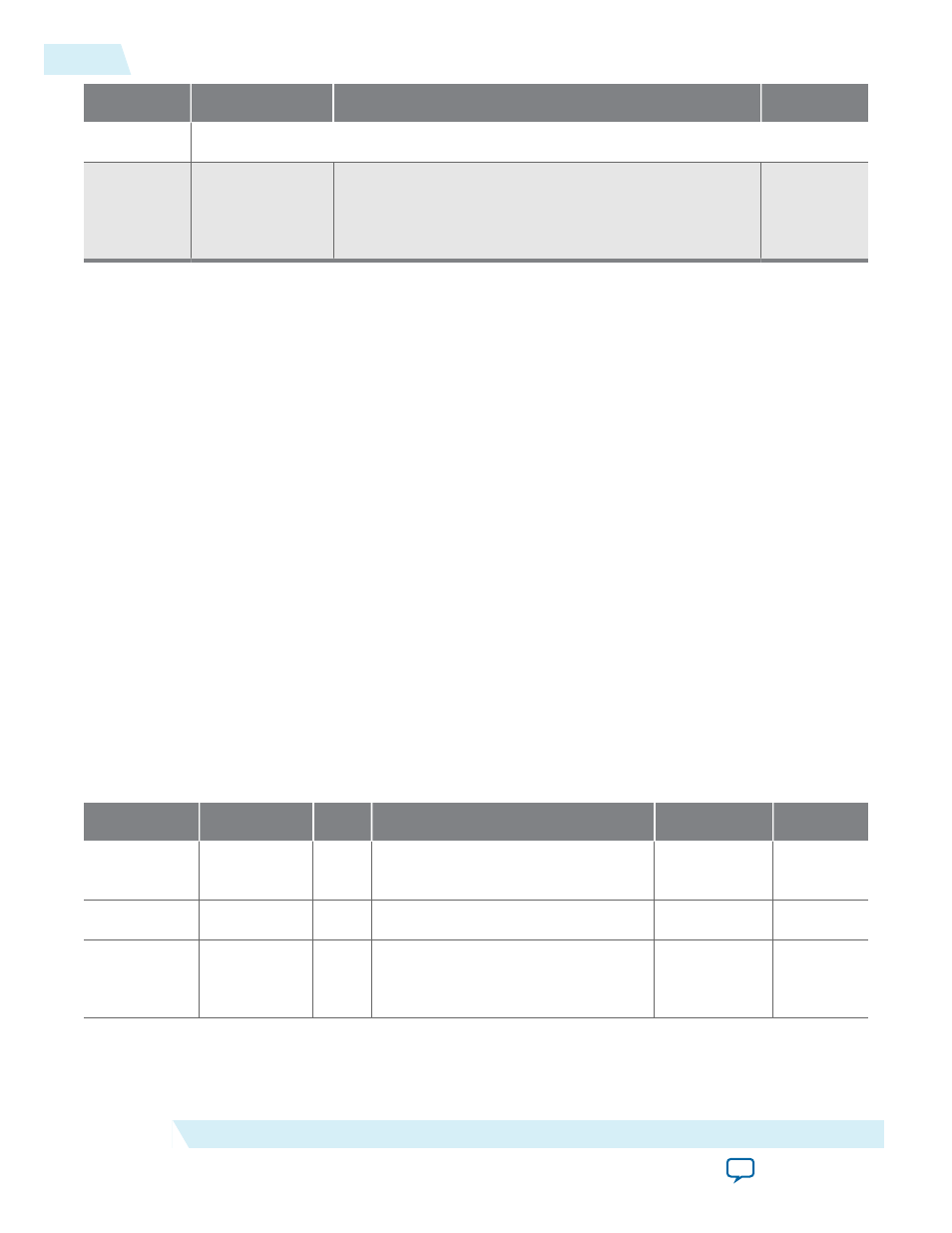

Address

Name-

Description

Access

0x2B7

Reserved

0x2B8

CNTR_RX_FCS

Number of received packets with FCS errors. This register

maintains a count of the number of pulses on the

l

fcs_error

output signal in variations with a custom

streaming client interface (variations without adapters).

RO

Related Information

•

•

MAC Configuration and Filter Registers

For more information about the

MAC_CMD_config

register.

40‑100GbE Example Design Registers

The following sections describe the registers that are included in the 40-100GbE example design and are

not a part of the 40-100GbE IP core. These registers are not available in the example designs for the

40GBASE-KR4 IP core variations.

on page 3-116

2-Wire Serial Interface Registers

on page 3-118

Related Information

40-100GbE IP Core Example Design

Altera provides an example design with the 40-100GbE IP core. This example design is ready for

compilation and can be configured on a target device. The listed registers are part of the example design.

PMD Registers

Table 3-50: PMD Control and Status Registers

The physical medium dependent (PMD) control and status registers allow you to turn on and determine the status

of the PMD device in the 40-100GbE IP core example design.

Address

Name

Bits

Description

HW Reset Value

Access

0x400

PMD_VERSION

[31:0] PMD revision. The character string is

“OPTs.”

0x4F505473

R

0x401

SCRATCH_PMD

[31:0] Scratch register available for testing.

0x00000000

RW

0x402

PMD_CMD_

CONFIG

[0]

Writing a 1 enables the PMD. When

you set this register to the value of 1,

the IP core seeks RX lock.

0x00000000

RW

3-116

40‑100GbE Example Design Registers

UG-01088

2014.12.15

Altera Corporation

Functional Description