Files generated for the 40-100gbe ip core, Simulating the ip core, Files generated for the 40-100gbe ip core -10 – Altera 40-Gbps Ethernet MAC and PHY MegaCore Function User Manual

Page 32: Simulating the ip core -10

•

Provides a list of IP core variations (parameter value choices) for which the Quartus II software can

generate a testbench and example design if you turn on Generate example design.

Files Generated for the 40-100GbE IP Core

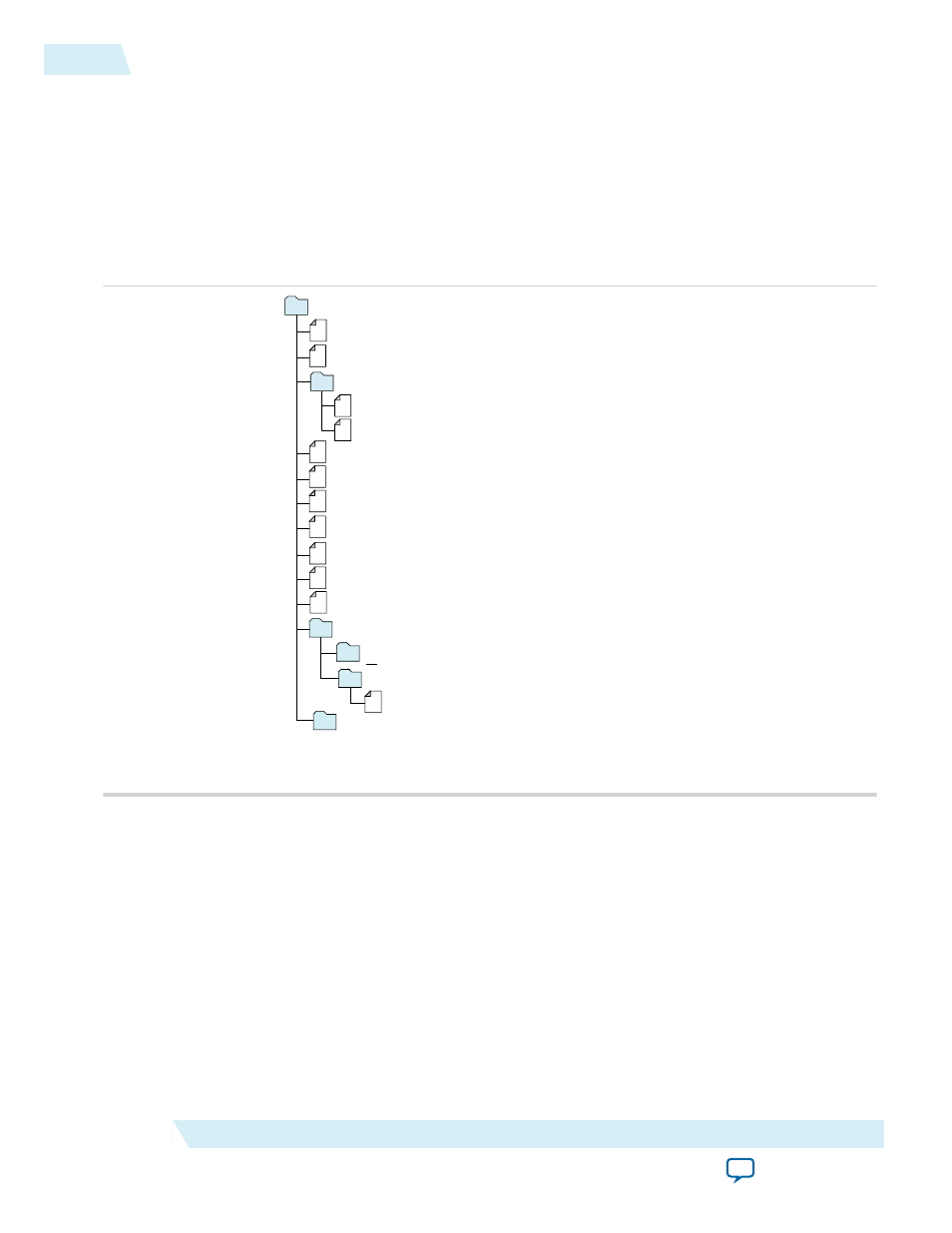

The Quartus II software version 14.1 generates the following output for your 40-100GbE IP core.

Figure 2-2: IP Core Generated Files

Notes:

1. If generated for your IP variation

_example

- Testbench and example project1

Simulating the IP Core

You can simulate your 40GbE or 100GbE IP core variation with the functional simulation model and the

testbench or example design generated with the IP core. The functional simulation model is a cycle-

accurate model that allows for fast functional simulation of your IP core instance using industry-standard

VHDL or Verilog HDL simulators. If your IP core variation does not generate a matching testbench, you

can create your own testbench to exercise the IP core functional simulation model.

The functional simulation model and testbench files are generated in project subdirectories. These

directories also include scripts to compile and run the example design.

Note: Use the simulation models only for simulation and not for synthesis or any other purposes. Using

these models for synthesis creates a nonfunctional design.

2-10

Files Generated for the 40-100GbE IP Core

UG-01088

2014.12.15

Altera Corporation

Getting Started