Mac address registers – Altera 40-Gbps Ethernet MAC and PHY MegaCore Function User Manual

Page 154

•

40-100GbE IP Core Preamble Processing

Describes the RX preamble pass-through feature and the effect of bit [0] of the

Preamble Pass-

Through Configuration

register on IP core behavior.

•

Inter-Packet Gap Generation and Insertion

on page 3-5

Information about the effects of the

IPG_DEL_PERIOD

register and the

IPG_DEL_ENABLE

register on IP

core behavior.

MAC Address Registers

All MAC addresses are stored in 2 words of 24 bits (3 bytes) in natural reading order. For example, an

Altera Device ID of 00-07-ED-11-22-33 is stored with the more significant word set to 24’h0007ED and

the least significant word set to 24’h112233.

The following table describes the MAC address registers. Additional information about the

MADDR_CTRL

register follows the table.

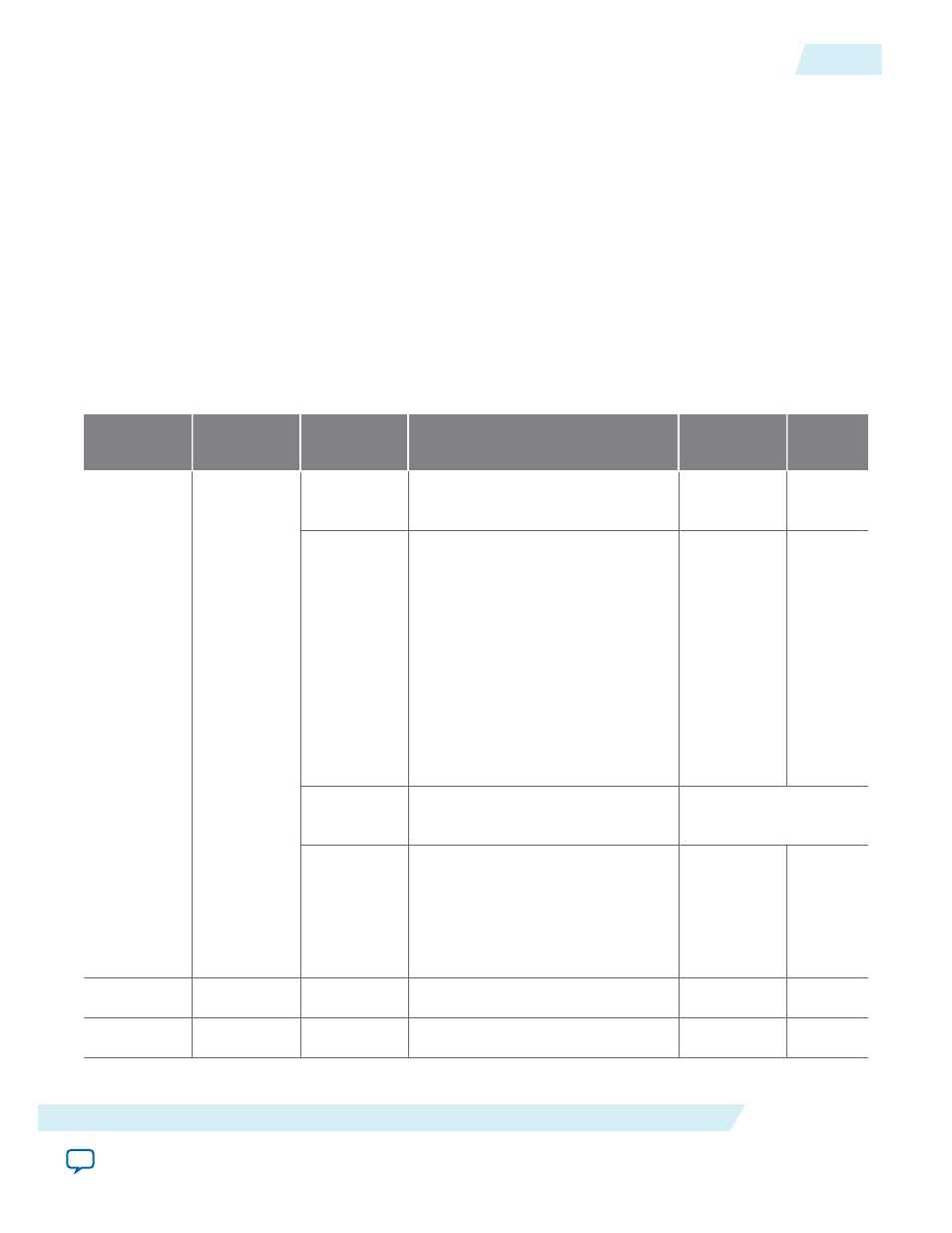

Table 3-46: MAC Address Registers

Address

Name

Bit

Description

HW Reset

Value

Access

0x140

MADDR_CTRL

[31]

When set to 1, the source address is

Inserted in TX packets.

1’b0

RW

[30]

When set to 1, enables the IP core to

check the destination address in RX

packets. When set to 0, all RX packets

are considered to have a matching

destination address.

If you enable destination address

filtering, by setting bit 0 of the

RX_

FILTER_CTRL

register (offset 0x103)

to the value of 0, but this bit, bit 30 of

the

MADDR_CTRL

register, is also set to

the value of 0, the IP core considers

all destination addresses to match.

1’b0

RW

[29:1]

Reserved.

0x0000000

0

[0]

When set to 1, enables destination

address 0x160-0x161 checking. If this

bit has the value of 0 and bit 30 has

the value of 1, the IP core considers

all destination addresses to not

match.

1’b0

RW

0x141

SRC_AD_LO

[23:0]

Source address (lower 24 bits).

0x00FF1234

RW

0x142

SRC_AD_HI

[23:0]

Source address (upper 24 bits).

0x000007ED RW

UG-01088

2014.12.15

MAC Address Registers

3-107

Functional Description

Altera Corporation