Mac configuration and filter registers – Altera 40-Gbps Ethernet MAC and PHY MegaCore Function User Manual

Page 146

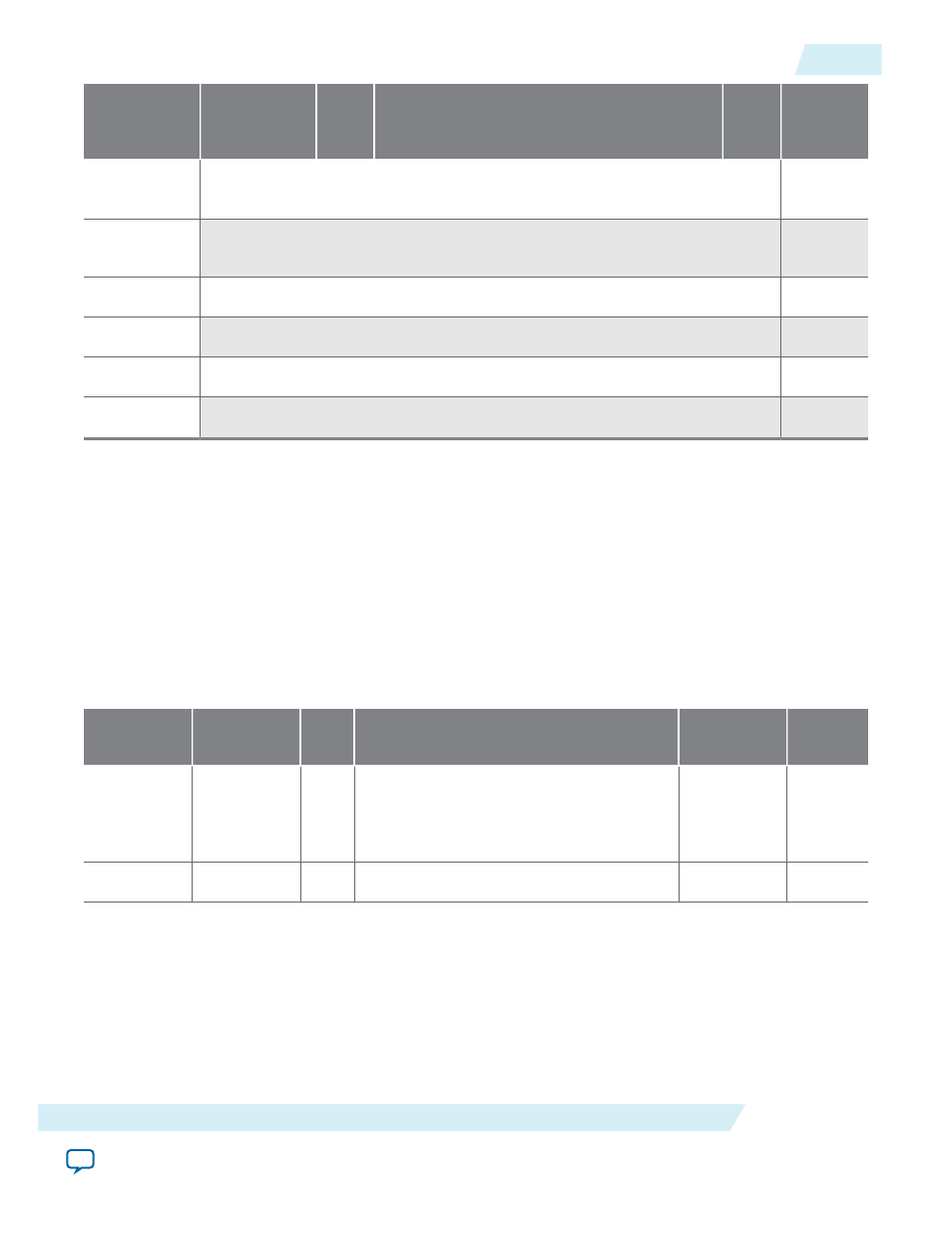

Address

Name

Bit

Description

HW

Reset

Value

Access

0xE6

This register is the equivalent of register 0xD5 for Lane 2 link training. (Refer to

10GBASE-KR PHY Register Definitions

).

RO

0xE7

This register is the equivalent of register 0xD6 for Lane 2 link training. (Refer to

10GBASE-KR PHY Register Definitions

).

RW

0xE8

This register is the equivalent of register 0xD3 for Lane 3 link training.

RW

0xE9

This register is the equivalent of register 0xD4 for Lane 3 link training.

R / RW

0xEA

This register is the equivalent of register 0xD5 for Lane 3 link training.

RO

0xEB

This register is the equivalent of register 0xD6 for Lane 3 link training.

RW

Related Information

The 40GBASE-KR4 variations of the 40-100GbE IP core use the 10GBASE-KR PHY IP core PHY registers

at internal offsets 0xB0–0xFF (at IP core register map offsets 0xB0–0xFF), in addition to the registers

listed in this section. Information about this PHY IP core, including register descriptions, is available in

the Backplane Ethernet 10GBASE-KR PHY IP Core with FEC Option chapter of the Altera Transceiver

PHY IP Core User Guide..

MAC Configuration and Filter Registers

Table 3-41: General MAC Control Registers

Describes the MAC configuration and filter registers.

Address

Name

Bit

Description

HW Reset

Value

Access

0x100

MAC_VERSION

[31:0] 40GbE/100GbE MAC IP core revision.

0x00DF1310

(40GbE)

0x00DD1310

(100GbE)

RO

0x101

SCRATCH_MAC

[31:0] Scratch register available for testing.

0x00000000

RW

UG-01088

2014.12.15

MAC Configuration and Filter Registers

3-99

Functional Description

Altera Corporation