2‑wire serial interface registers, Wire serial interface registers – Altera 40-Gbps Ethernet MAC and PHY MegaCore Function User Manual

Page 165

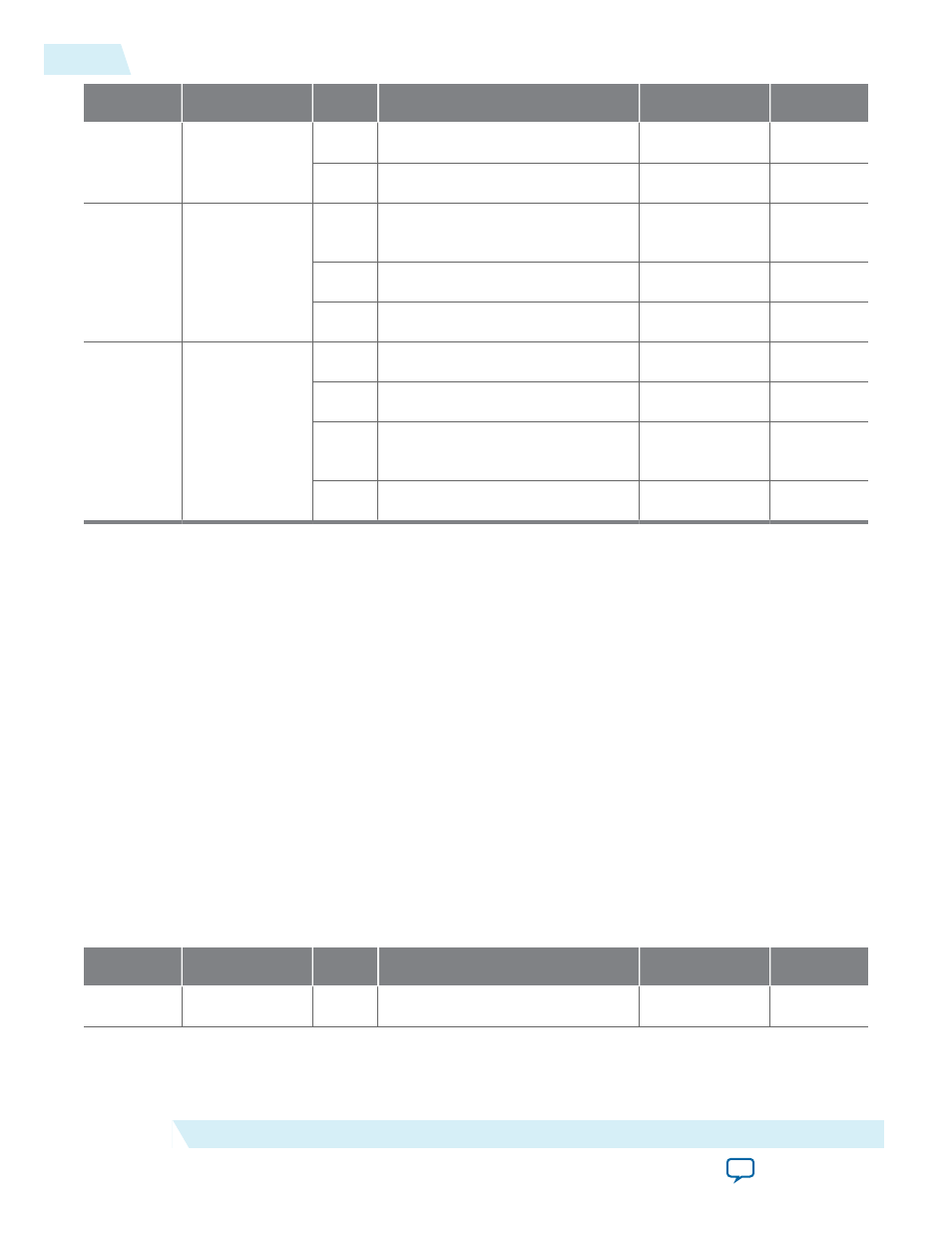

Address

Name

Bits

Description

HW Reset Value

Access

0x411

MDIO_RDATA

[31]

Link is busy.

1b’0

R

[15:0]

Result of previous read.

0x0000

R

0x412

MDIO_ADDR

[14:10] PHY address driven to external

module.

5’h00

RW

[9:5]

PHY address to access.

5’h00

RW

[4:0]

DEV address.

5’h01

RW

0x413

MDIO_CMD

[3]

Address of the register to be written. 1b’0

RW

[2]

Write signal.

1b’0

RW

[1]

Address of the register to read. This

address post increments.

1b’0

RW

[0]

Read signal.

1b’0

RW

Related Information

40-100GbE IP Core Example Design

Altera provides an example design with the 40-100GbE IP core. This example design is ready for

compilation and can be configured on a target device. The listed registers are part of the example design.

2‑Wire Serial Interface Registers

Several optical modules use the 2-wire serial interface protocol, which requires only limited resources.

This interface uses two, bidirectional open-drain lines, a serial data line (SDA) and a serial clock (SCL).

The master node drives the clock and addresses slaves. Data is sent most significant bit first. The slave

node receives the clock and address. Unlike the MDIO protocol, the 2-wire serial interface can include

multiple masters. In addition, the master and slave roles may be changed after a STOP message is sent.

The interface has an eight-bit address space, so a maximum of 255 nodes can communicate. The interface

runs at 400 KHz.

Table 3-52: 2‑Wire Serial Interface Registers

Describes the 2-wire serial registers in the 40-100GbE IP core example design. Refer to the datasheet for your

2-wire device for more information.

Note: The 2-wire serial interface in the IP core example design does not support the specialized CRC-8 check or

multibyte transaction modes.

Address

Name

Bits

Description

HW Reset Value

Access

0x420

2WS_WDATA

[7:0]

Data to be written.

0x00

RW

3-118

2‑Wire Serial Interface Registers

UG-01088

2014.12.15

Altera Corporation

Functional Description