Altera 40-Gbps Ethernet MAC and PHY MegaCore Function User Manual

Page 62

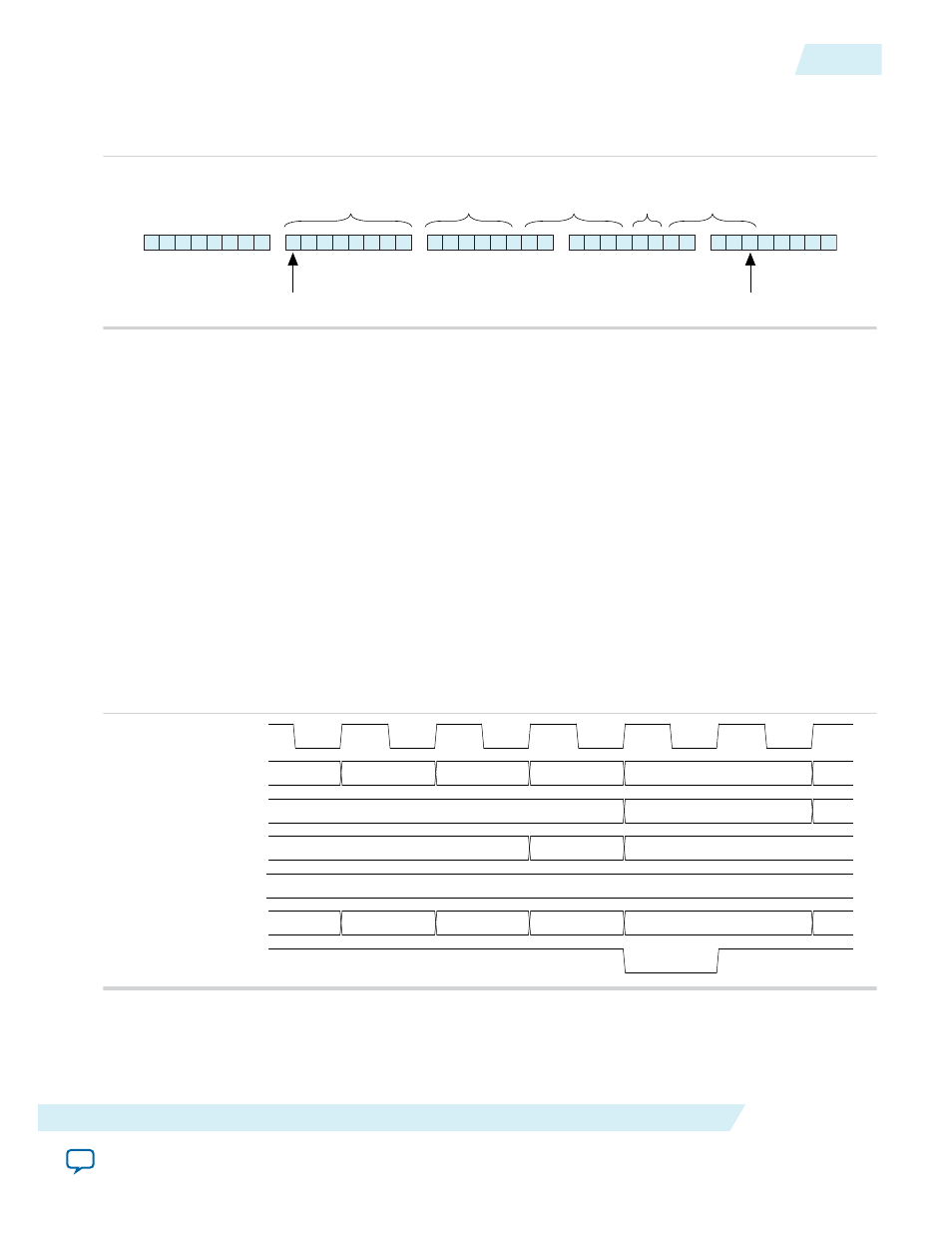

Figure 3-12: Short TX Packet Example With Preamble

Illustrates the transmission of a short packet for the 100GbE IP core when preamble pass-through is

turned on.

First data

Destination

MAC addr

Source

MAC Addr

Total

length

Last data

“hello”

Preamble,

including Start (ignored)

and SFD

Example 3-4: Bus Representation of a Short TX Packet With Preamble

This example shows the Verilog HDL code that represents the simple packet illustrated in the

preceding figure. Note that bit

din_end[5]

corresponding to the “Last data” in the figure, is

asserted.

wire [8*8-1:0] preamble = 64’hXX55_5555_55D5;

wire [6*8-1:0] dst_addr = 48’hffff ffff ffff;

wire [6*8-1:0] src_addr = 48’h0007 edff 1234;

wire [2*8-1:0] len = 16’d64;

din = {64’h0, preamble, dst_addr, src_addr, len, “hello”, 40’h0};

din_start = 5’b01000;

din_end = 40’b00000000_00000000_00000000_00000000_00100000;

Figure 3-13: Sample 100GbE IP Core TX Bus Activity

Illustrates the deassertion of the

din_ack

signal. The data beginning with 0x0202 is not immediately

accepted. The

din

bus must be held until

din_ack

returns to one. At this point normal data flow resumes.

e100_tb.dut.clk_txmac

e100_tb.dut.din[207:0]

e100_tb.dut.din_start[4:0]

e100_tb.dut.din_end_pos[39:0]

e100_tb.dut.dout_d[319:0]

e100_tb.dut.din[111:0]

e100_tb.dut.din_ack

E8E9EAEBECE

101112131415...

38393A3B3C3D...

606162636465...

020202020202010101010101011...

00

00

10

0000000400

020304050607

2A2B2C2D2E2F...

525354555657...

7A7B7C7DCCC...

88898A8B8C8D8E8F909192939495

The TX logic supports packets of less than the usual length. However, no more than two start-of-packets

can occur in the same clock cycle.

UG-01088

2014.12.15

100GbE IP Core Without Adapters

3-15

Functional Description

Altera Corporation