Altera 40-Gbps Ethernet MAC and PHY MegaCore Function User Manual

Page 128

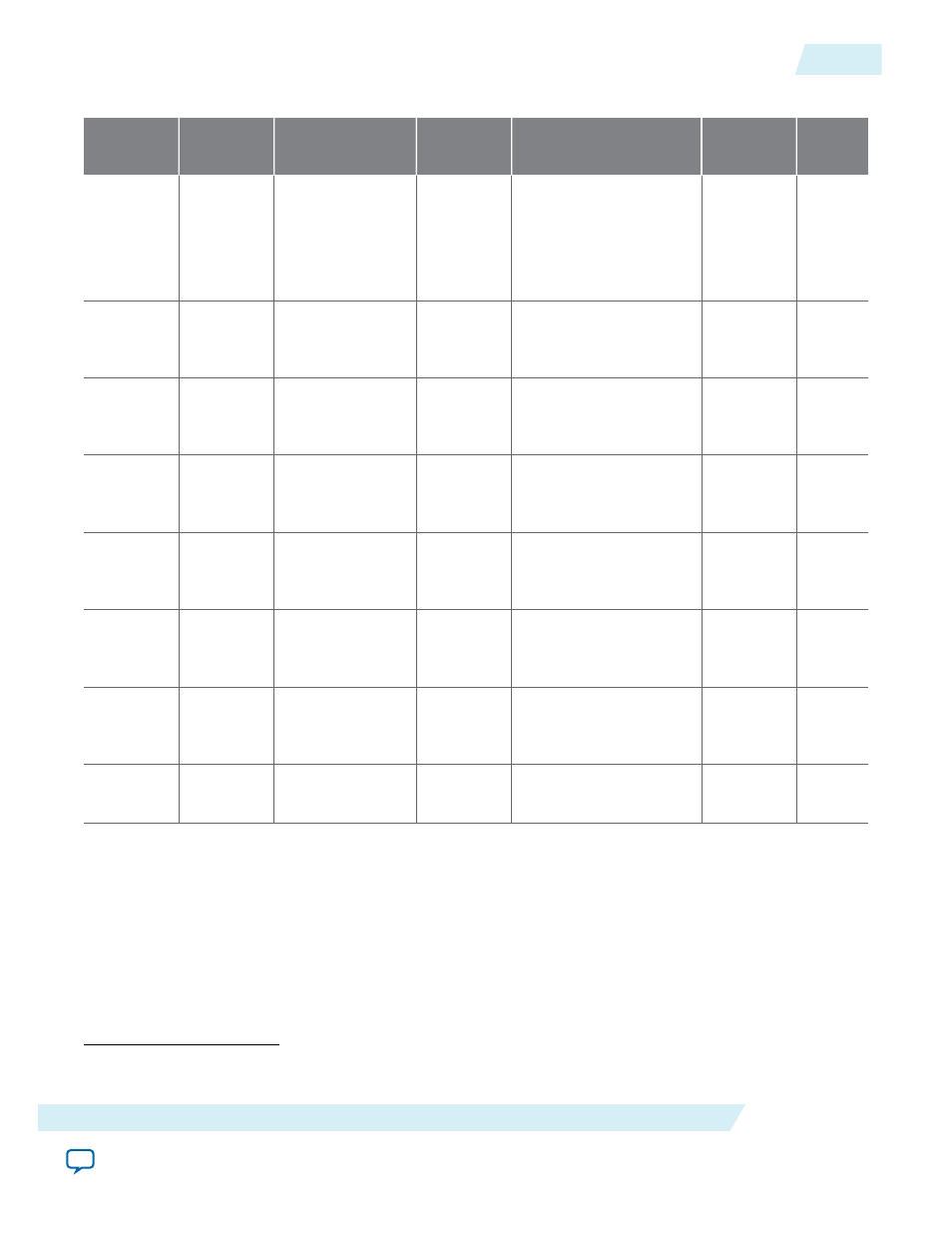

Table 3-26: Scratch and Clock Registers for Applicable Devices

Address

Name

Applicable

Device(s)

Bit

Description

HW Reset

Value

Access

0x000

PHY_

VERSION

Arria V GZ,

Stratix IV, and

Stratix V

[31:0]

40GbE/100GbE PHY IP

core revision.

0x00E01310

(40GbE)

0x

00DE1310

(100GbE)

R

0x001

SCRATCH_

PHY

Arria V GZ,

Stratix IV, and

Stratix V

[31:0]

Scratch register available

for testing.

0x00000000 RW

0x002

(12)

CLK_TXS

Arria V GZ,

Stratix IV, and

Stratix V

[19:0]

TX serial clock rate

monitor in KHz.

0x00000

R

0x003

(12

)

CLK_RXS

Arria V GZ,

Stratix IV, and

Stratix V

[19:0]

RX serial clock rate

monitor in KHz.

0x00000

R

0x004

CLK_TXC

Arria V GZ,

Stratix IV, and

Stratix V

[19:0]

TX core clock rate

monitor in KHz.

0x00000

R

0x005

CLK_RXC

Arria V GZ,

Stratix IV, and

Stratix V

[19:0]

RX core clock rate

monitor in KHz.

0x00000

R

0x006

—

Arria V GZ,

Stratix IV, and

Stratix V

–

Reserved.

—

—

0x007

—

Arria V GZ and

Stratix V

–

Reserved.

—

—

(12)

When the line rate is 10.3125 Gbps, the frequency of the serial clocks

clk_tx_serial

and

clk_rx_serial

is

10312.5/40 = 257.8125 MHz.

UG-01088

2014.12.15

Transceiver PHY Control and Status Registers

3-81

Functional Description

Altera Corporation