Altera 40-Gbps Ethernet MAC and PHY MegaCore Function User Manual

Page 95

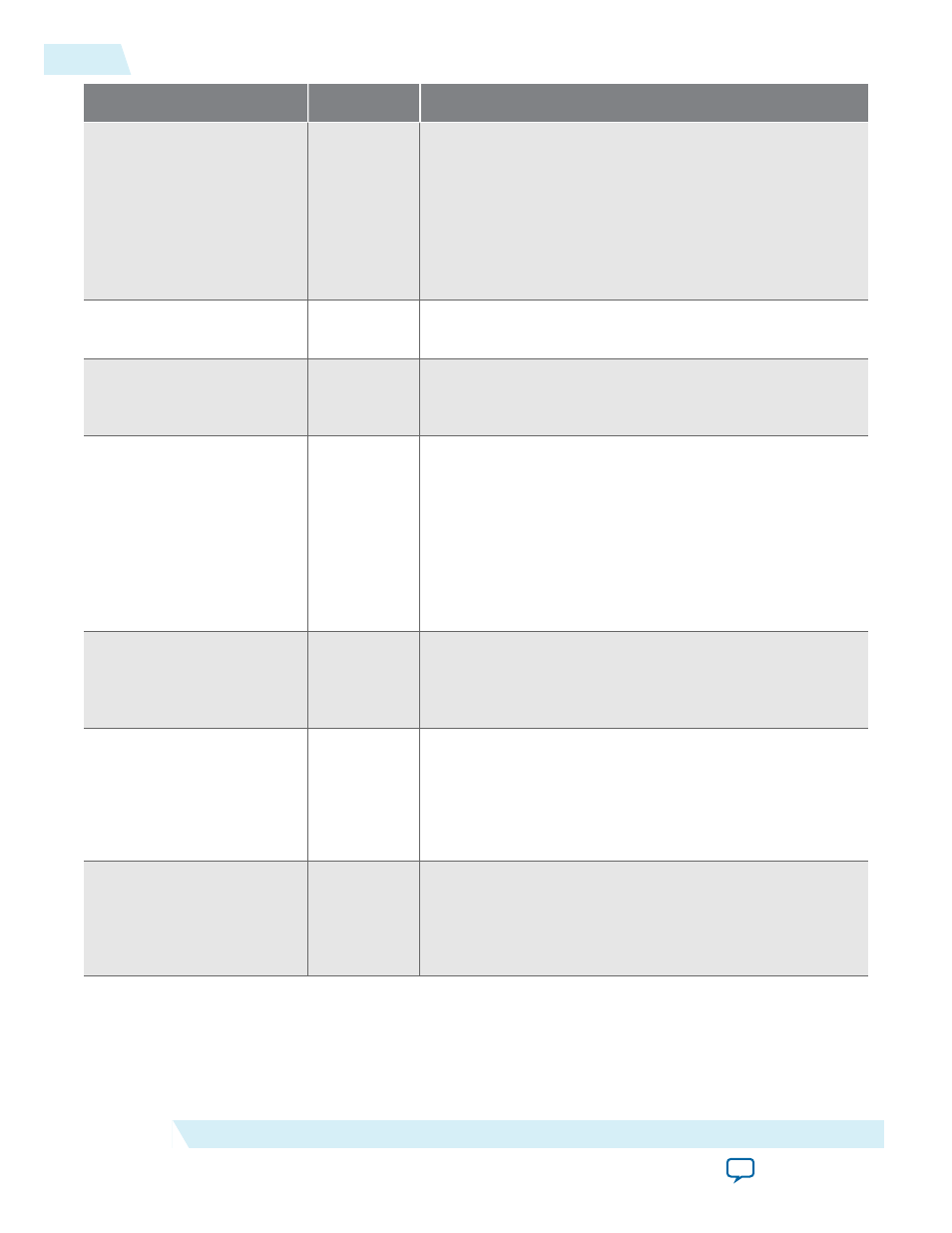

Signal Name

Direction

Description

tap_to_upd[11:0]

Output

Specifies the TX equalization tap to update to optimize

signal quality. Each lane's field has the following valid

values:

• 3'b100: main tap

• 3'b010: post-tap

• 3'b001: pre-tap

This signal is present only if link training is enabled.

seq_start_rc[3:0]

Output

When a bit is asserted, starts PCS reconfiguration for the

corresponding lane.

dfe_start_rc[3:0]

Output

When a bit is asserted, starts RX DFE equalization for the

corresponding lane. This signal is present only if RX

equalization is enabled.

dfe_mode[7:0]

Output

Specifies the DFE operation mode. Valid at the rising edge

of the

def_start_rc

signal and held until the falling edge of

the

rc_busy

signal. The following encodings are defined for

each lane:

• 2'b00: Disable DFE

• 2'b01: DFE triggered mode (single shot)

• 2b10 and 2'b11 are reserved.

This signal is present only if RX equalization is enabled.

ctle_start_rc[3:0]

Output

When a bit is asserted, starts continuous time-linear

equalization (CTLE) reconfiguration on the corresponding

lane. This signal is present only if RX equalization is

enabled.

ctle_rc[15:0]

Output

RX CTLE value. This signal is valid at the rising edge of the

ctle_start_rc

signal and held until the falling edge of the

rc_busy

signal. The valid range of values is 4'b0000–

4'b1111. 4'b0000 indicates the RX CTLE is disabled and

4'b1111 indicates RX CTLE is at its maximum value. This

signal is present only if RX equalization is enabled.

ctle_mode[7:0]

Output

Specifies the CTLE mode. This signal is valid at the rising

edge of the

ctle_start_rc

signal and held until the falling

edge of the

rc_busy

signal. The only valid value of this

signal in the 40-100GbE IP core is 2'b0. This signal is

present only if RX equalization is enabled.

3-48

40GBASE-KR4 Reconfiguration Interface

UG-01088

2014.12.15

Altera Corporation

Functional Description