Software interface: registers, Software interface: registers -76 – Altera 40-Gbps Ethernet MAC and PHY MegaCore Function User Manual

Page 123

•

on page 3-43

Describes the

lanes_deskewed

PHY output signal.

•

MAC to PHY Connection Interface

on page 3-43

•

External Reconfiguration Controller

Software Interface: Registers

This section provides information about the memory-mapped registers. You access these registers using

the IP core control and status interface. The registers use 32-bit addresses; they are not byte addressable.

Write operations to a read-only register field have no effect. Read operations that address a Reserved

register return an unspecified constant. Write operations to Reserved registers have no effect. Accesses to

registers that do not exist in your IP core variation have an unspecified result.

The following tables list the memory mapped registers for the 40-100GbE IP core and the memory

mapped registers for the 40-100GbE IP core example design.

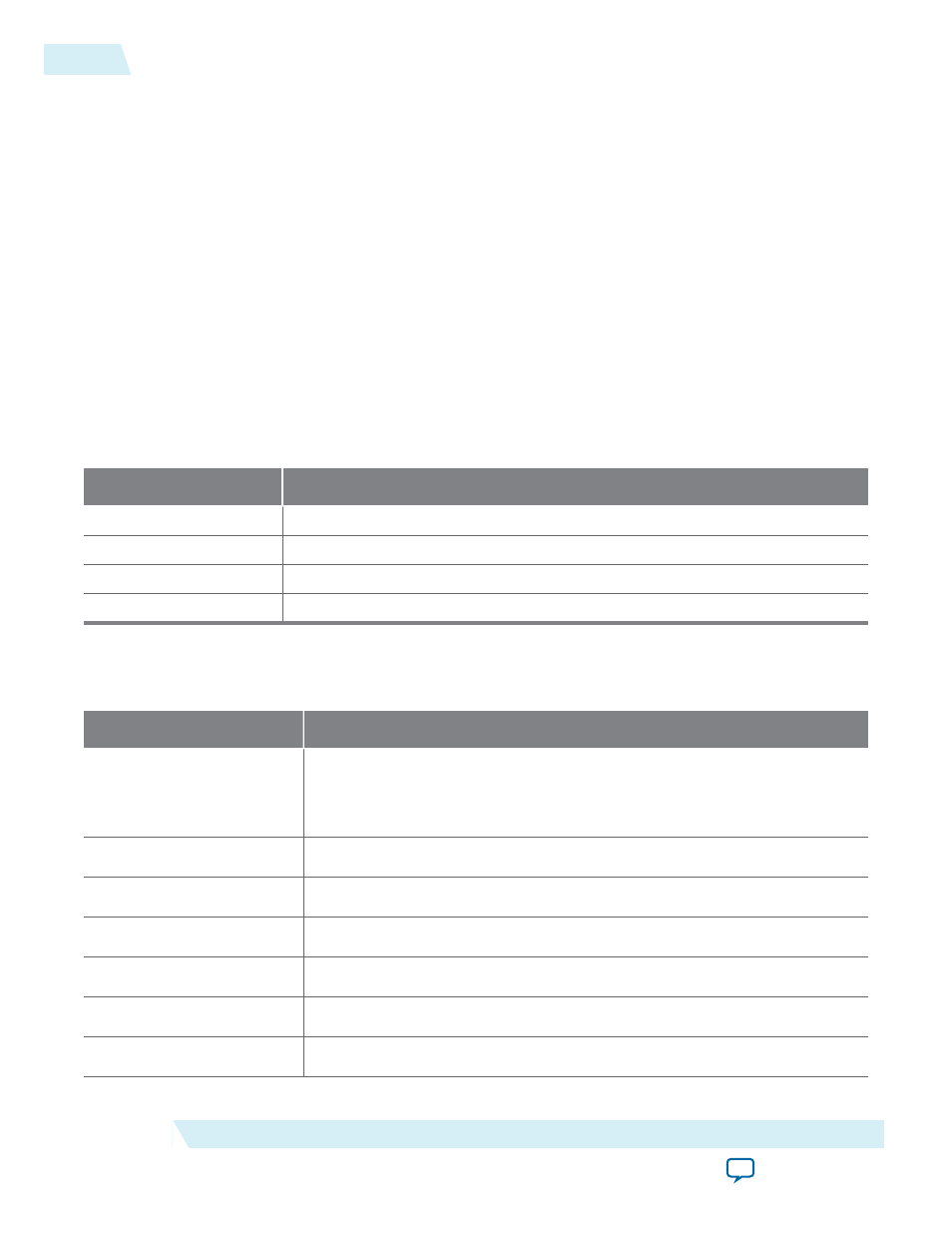

Table 3-23: 40-100GbE IP Core Register Map Overview

Lists the main ranges of the memory mapped registers for the 40-100GbE IP core.

Word Offset

Register Category

0x0–0x3F

PCS registers

0x40–0x7F

Low Latency PHY IP core registers

0x80–0xFF

40GBASE-KR4 registers

0x100 and above

40-100GbE IP core MAC and example design registers

Table 3-24: 40-100GbE IP Core Address Map

Lists the memory mapped registers for the 40-100GbE IP core. Each register is 32 bits, and the addresses (word

offsets) each address a full word.

Word Offset

Register Description

0x000–0x009

Transceiver PHY control and status registers. Some of these registers are

available only for Stratix IV devices.

These registers are not the Altera transceiver PHY IP core registers.

0x00A–0x00F

Reserved.

0x010–0x014

Lock status registers.

0x015–0x016

Bit error flag registers.

0x017

PCS hardware error register.

0x018

BER monitor register.

0x019

Test mode register.

3-76

Software Interface: Registers

UG-01088

2014.12.15

Altera Corporation

Functional Description