Altera 40-Gbps Ethernet MAC and PHY MegaCore Function User Manual

Page 125

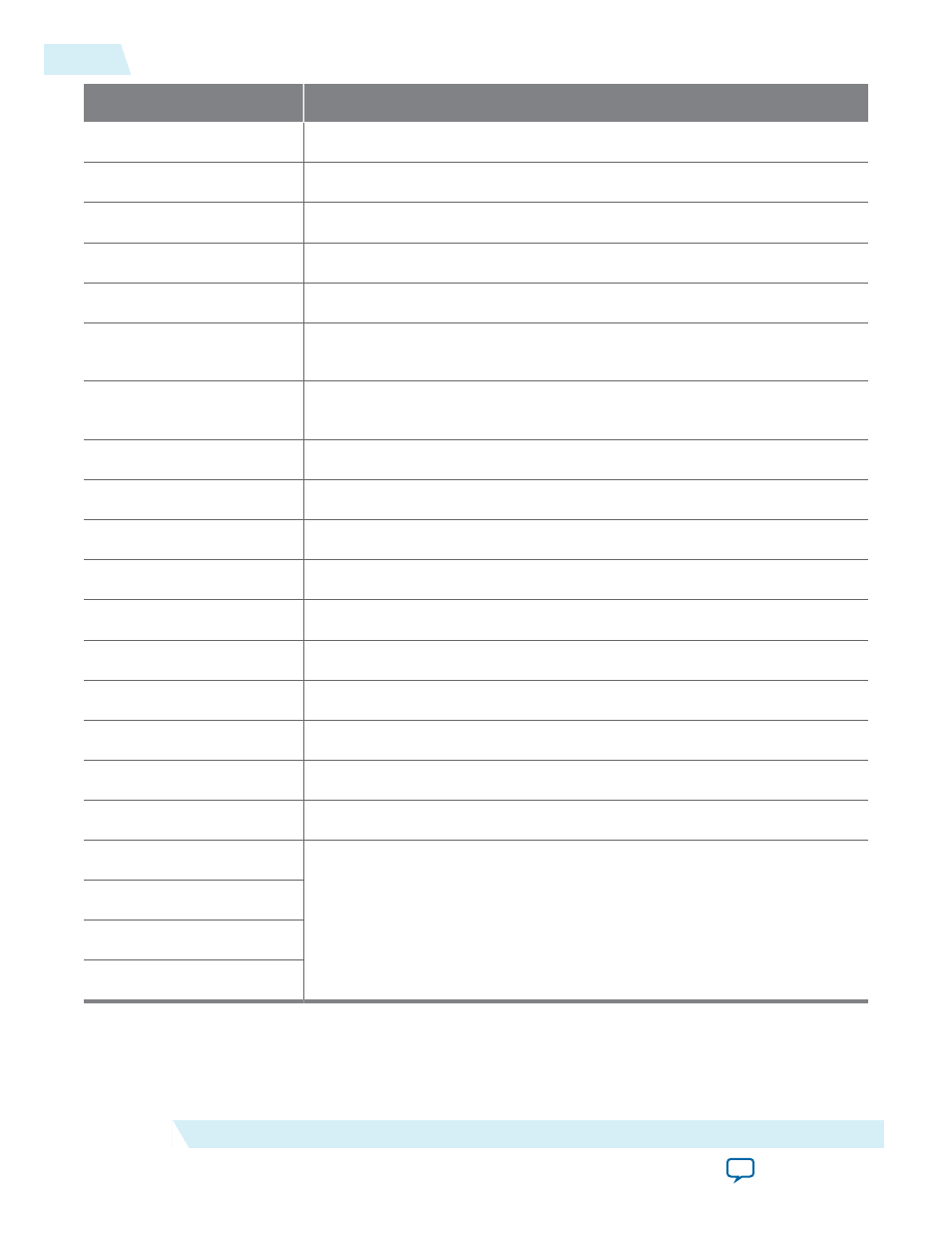

Word Offset

Register Description

0x118–0x11F

Reserved.

0x120

MAC hardware error register.

0x121

MAC reset register.

0x122

One of two link fault signaling registers.

0x123

CRC configuration register.

0x124

Padding configuration register. One of the MAC feature configuration

registers.

0x125

Preamble pass-through configuration register. One of the MAC feature

configuration registers.

0x126–0x127

IPG adjustment registers. Two of the MAC feature configuration registers.

0x140–0x17F

MAC address registers.

0x180–0x1FF

Reserved.

0x200–0x229

Transmit side statistics registers that are not TX packet statistics registers.

0x22A–0x22D

TX Packet Statistics.

0x22E–0x27F

Reserved.

0x280–0x2A9

Receive side statistics registers that are not RX packet statistics registers.

0x2AA–0x2B8

RX packet statistics registers.

0x2B9–0x3FF

Reserved.

0x400–0x423

40-100GbE example design registers. Refer to the following table.

0x800-0x9FF

Altera’s Low Latency PHY IP core registers, for use with the CAUI-4

configuration only. Offsets 0x800-0x9FF are for CAUI-4 lane 1, offsets

0xA00-0xBFF are for CAUI-4 lane 2, offsets 0xC00-0xDFF are for CAUI-4

lane 3, and offsets 0xE00-0xFFF are for CAUI-4 lane 4. Each lane maps to

word addresses 0x000-0x1FF for one low latency PHY transceiver channel.

0xA00-0xBFF

0xC00-0xDFF

0xE00-0xFFF

3-78

Software Interface: Registers

UG-01088

2014.12.15

Altera Corporation

Functional Description