Bit error flag registers – Altera 40-Gbps Ethernet MAC and PHY MegaCore Function User Manual

Page 133

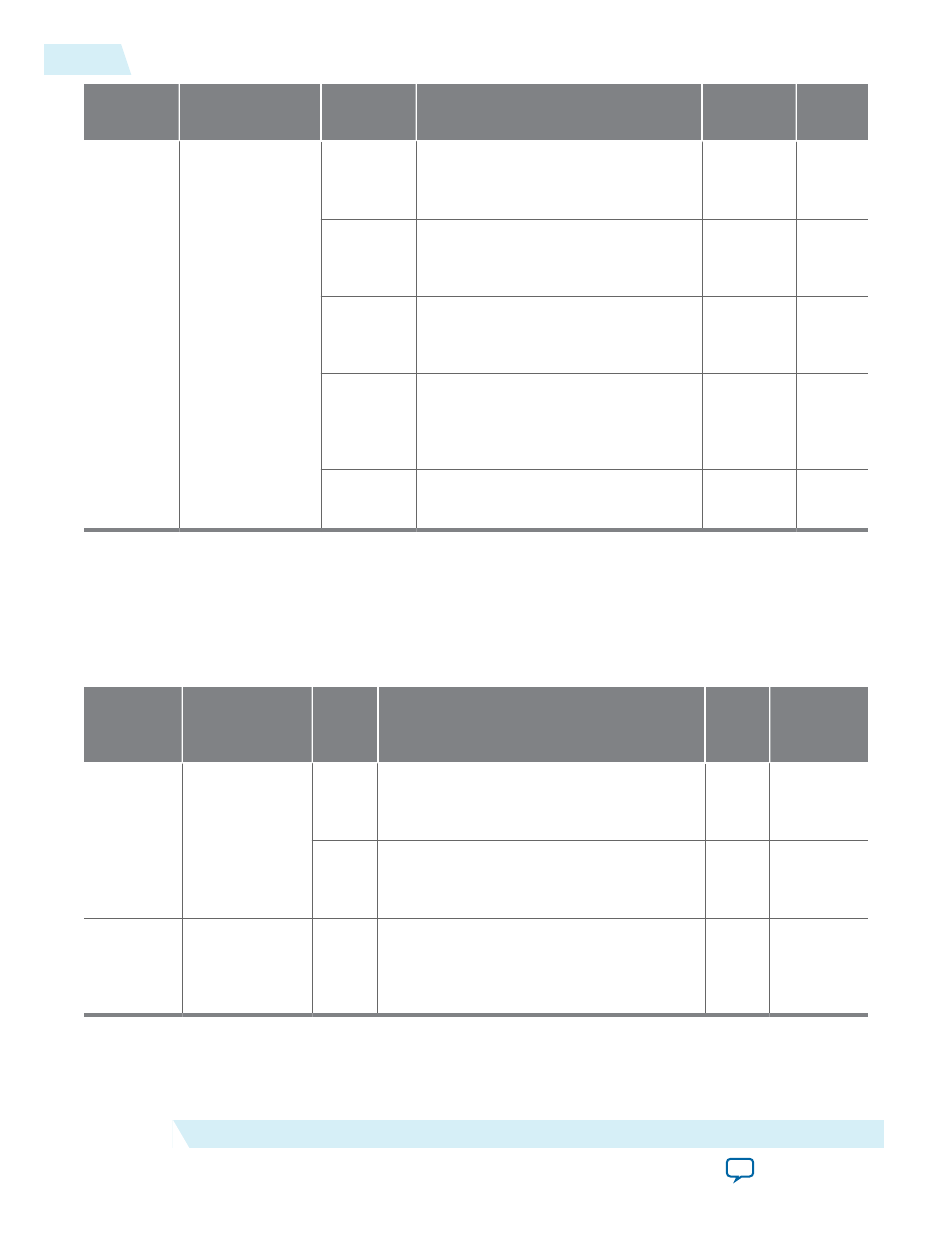

Address

Name

Bit

Description

HW Reset

Value

Access

0x014

RX_AGGREGATE

[4]

When asserted, indicates a change in

PCS-VLANE permutation. This status

bit clears on read.

1’b0

R

[3]

When asserted, indicates a change in

lanes deskewed status. This status bit

clears on read.

1’b0

R

[2]

When asserted, indicates a change in

PCS-VLANE tag drop position. This

status bit clears on read.

1’b0

R

[1]

When asserted, indicates that all lanes

are locked and lane-to-lane deskew is

complete so that the 40-100GbE IP core

is in operating normally.

1’b0

R

[0]

When asserted, indicates that all lanes

are word and alignment marker locked.

1b’0

R

Bit Error Flag Registers

Bit errors occur naturally from time to time on high speed serial links. The higher level Ethernet protocol

includes mechanisms to respond to errors and tally them appropriately. These lower level flags are useful

for tracking errors in a physical link and computing error rates.

Table 3-29: Bit Error Flag Registers

Address

Name

Bit

Description

HW

Reset

Value

Access

0x015

FRAMING_ERR

[31]

When asserted, indicates that a framing error

has occurred on any lane. This status bit

clears on read.

1’b0

R

[19:0]

When asserted, indicates that a framing error

has occurred on the corresponding physical

lane. This status bit clears on read.

0x0000

0

R

0x016

BIP_ERR

[19:0]

When asserted, indicates that a BIP (lane

parity) error has occurred on the

corresponding physical lane. This status bit

clears on read.

0x0000

0

R

3-86

Bit Error Flag Registers

UG-01088

2014.12.15

Altera Corporation

Functional Description