Altera 40-Gbps Ethernet MAC and PHY MegaCore Function User Manual

Page 142

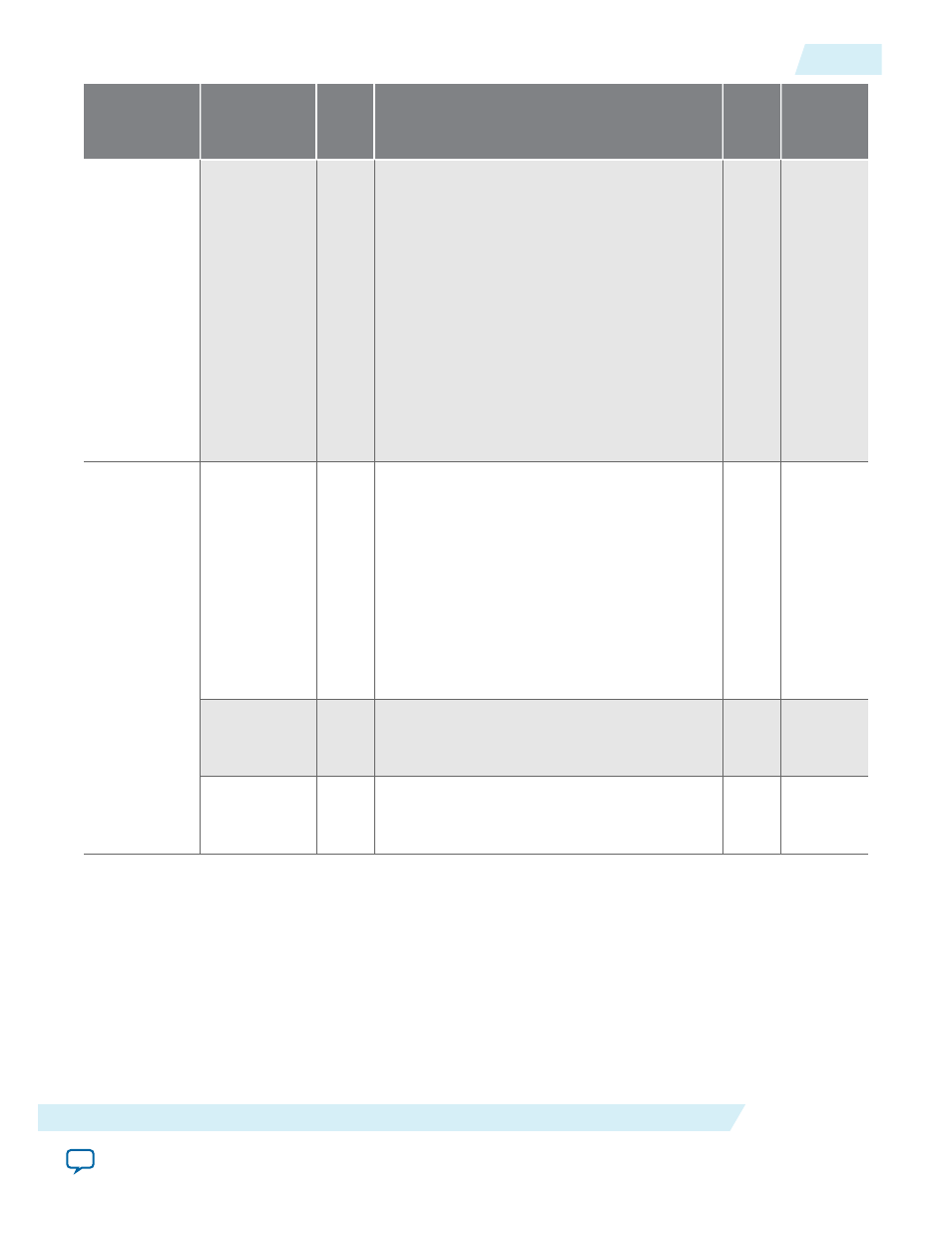

Address

Name

Bit

Description

HW

Reset

Value

Access

0x0CC

Override AN

Channel

Select

[3:0]

If you set the value of the Override AN Channel

Enable register field (0xC0[6]) to the value of 1,

then while 0xC0[6] has the value of 1, the value

in this register field (0xCC[3:0])overrides the

master channel you set with the Auto-Negotia‐

tion Master parameter.

This register field has the following valid values:

• 4'b0001: Selects Lane 0

• 4'b0010: Selects Lane 1

• 4'b0100: Selects Lane 2

• 4'b1000: Selects Lane 3

All other values are invalid. The new master

channel is encoded with one-hot encoding.

4'b0

RW

0x0D1

Restart Link

training,

Lane 1

[1]

When set to 1, resets the 40GBASE-KR4 start-up

protocol. When set to 0, continues normal

operation. This bit self clears. Refer to the state

variable

mr_restart_training

as defined in

Clause 72.6.10.3.1 and 10GBASE-KR PMD

control register bit (1.150.0) in IEEE Std 802.3ap-

2007.

Register bit 0xD1[0] refers to Lane 0. This bit is

the equivalent of register 0xD1[0] for Lane 1.

(Refer to

).

1'b0

RW

Restart Link

training,

Lane 2

[2]

This bit is the equivalent of register 0xD1[0] for

Lane 2. (Refer to

).

1'b0

RW

Restart Link

training,

Lane 3

[3]

This bit is the equivalent of register 0xD0[1] for

Lane 3. (Refer to

).

1'b0

RW

UG-01088

2014.12.15

40GBASE-KR4 Registers

3-95

Functional Description

Altera Corporation