Altera 40-Gbps Ethernet MAC and PHY MegaCore Function User Manual

Page 162

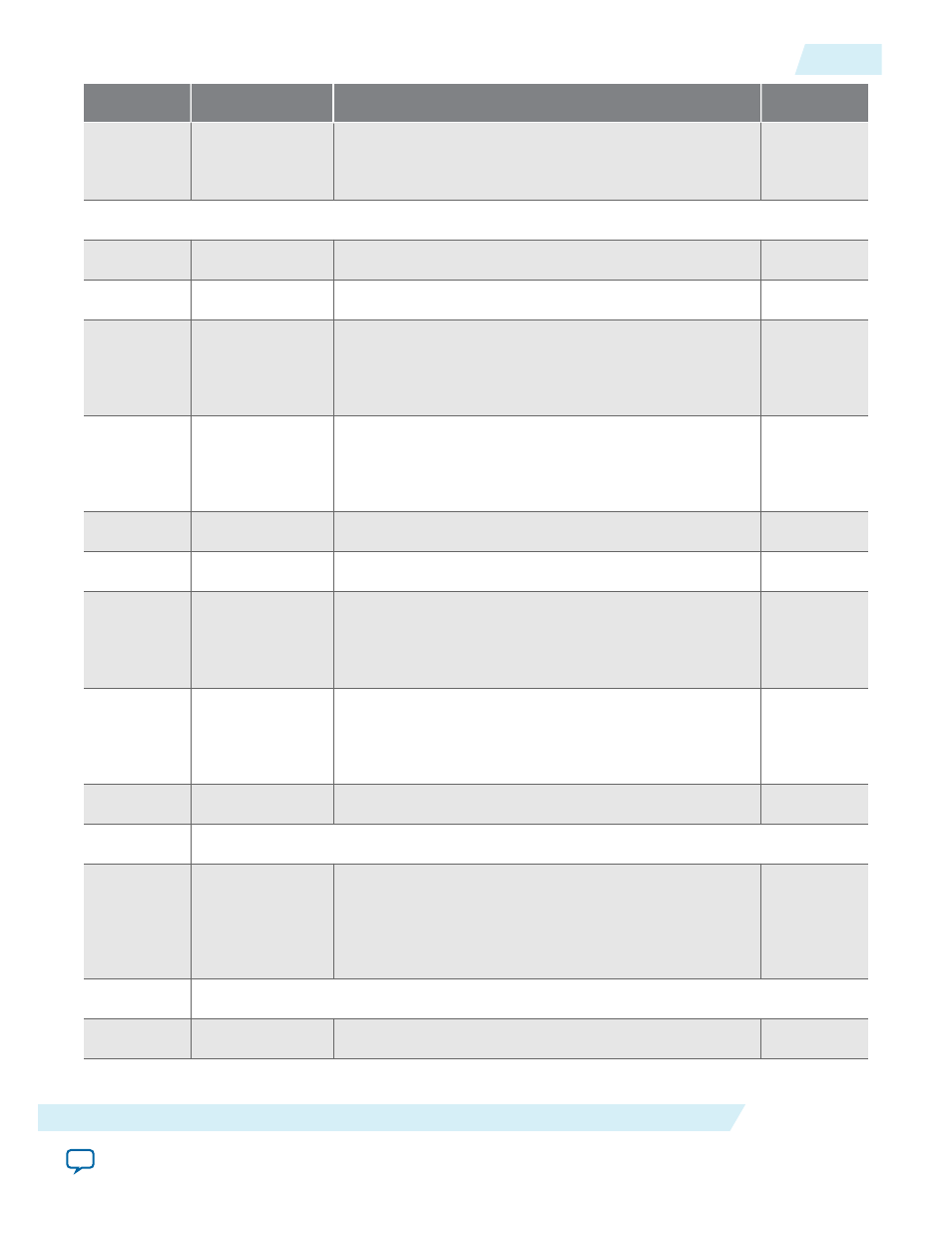

Address

Name-

Description

Access

0x2A9

CNTR_RX_CRCERR_

HI

Number of received frames between the length of 64 and the

value configured in 0x103 register with CRC error (upper 32

bits)

RO

RX Packet Statistics

0x2AA

CNTR_RX_ST_LO

Number of received frame starts (lower 32 bits)

RO

0x2AB

CNTR_RX_ST_HI

Number of received frame starts (upper 32 bits)

RO

0x2AC

CNTR_RX_DB_LO

Number of received data blocks (number of full symbols (2

or 5 words, depending on the variation) that pass from the

PHY to the MAC that contain at least some data) (lower 32

bits)

RO

0x2AD

CNTR_RX_DB_HI

Number of received data blocks (number of full symbols (2

or 5 words, depending on the variation) that pass from the

PHY to the MAC that contain at least some data) (upper 32

bits)

RO

0x2AE

CNTR_RXF_ST_LO

Number of accepted frame starts (lower 32 bits)

RO

0x2AF

CNTR_RXF_ST_HI

Number of accepted frame starts (upper 32 bits)

RO

0x2B0

CNTR_RXF_DB_LO

Number of accepted data blocks (number of full symbols (2

or 5 words, depending on the variation) that pass from the

PHY to the MAC that contain at least some data and that the

MAC accepts) (lower 32 bits)

RO

0x2B1

CNTR_RXF_DB_HI

Number of accepted data blocks (number of full symbols (2

or 5 words, depending on the variation) that pass from the

PHY to the MAC that contain at least some data and that the

MAC accepts) (upper 32 bits)

RO

0x2B2

CNTR_RXF_LONG

Number of packets aborted due to excessive length.

RO

0x2B3

Reserved

0x2B4

CNTR_RX_EBLK

Number of received blocks with XGMII and CGMII errors.

The number of received error blocks is equal to the RX

symbol error counter defined by Operation Administration

and Maintenance (OAM) in accordance with IEEE standard

802.3ba.

RO

0x2B5

Reserved

0x2B6

CNTR_RX_RUNT

Number of received runt packets

RO

UG-01088

2014.12.15

Statistics Registers

3-115

Functional Description

Altera Corporation