Prbs registers, 40gbase-kr4 registers – Altera 40-Gbps Ethernet MAC and PHY MegaCore Function User Manual

Page 139

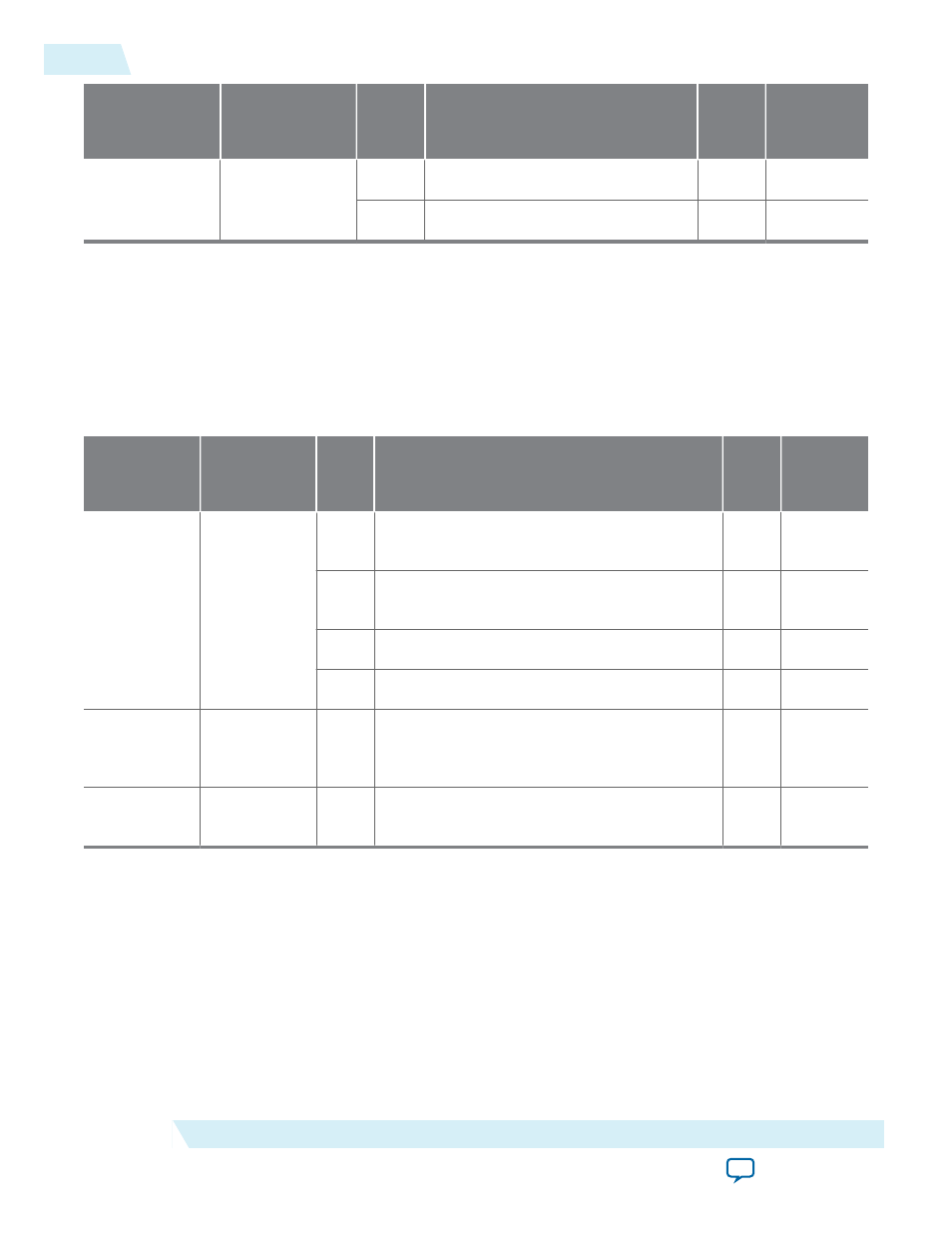

Address

Name

Bit

Description

HW

Reset

Value

Access

0x023

PCS

VLANE3

[9:5]

Virtual index for physical lane 19

5h’00

R

[4:0]

Virtual index for physical lane 18

5h’00

R

PRBS Registers

The PRBS feature operates on a per virtual lane basis. The PRBS streams are bit interleaved to form

10 Gbps lanes. PRBS transmissions are unframed.

Table 3-39: PRBS Registers

There is some deviation among manufacturers regarding the exact PRBS implementation on high rate Ethernet

equipment. If the PRBS is working properly in loopback but consistently wrong with a remote device, Altera

recommends that you confirm that the remote device is operating as described here.

Address

Name

Bit

Description

HW

Reset

Value

Access

0x030

PRBS_CTRL

[4]

When set to 1, selects PRBS-9 for the RX lane.

When set to 0, selects PRBS-31 for the RX lane.

1’b0

RW

[3]

When set to 1, selects PRBS-9 for the TX lane.

When set to 0, selects PRBS-31 for the TX lane.

1’b0

RW

[2]

When set to 1, enables the RX PRBS checker.

1’b0

RW

[1]

When set to 1, enables the TX PRBS transmitter. 1’b0

RW

0x031

PRBS_ERR_INJ

[19:0] When set to 1, injects an error in the

corresponding lane. This register is rising edge

triggered. Write 0 to clear.

20'b0 RW

0x032

PRBS_EFLAGS

[19:0] When set to 1, indicates a PRBS error in the

corresponding PCS-VLANE. Clears on read.

20'b0 R

40GBASE-KR4 Registers

Most 40GBASE-KR4 registers are 10GBASE-KR PHY registers of the 10GBASE-KR PHY IP core,

40GBASE-KR4 variations of the 40-100GbE IP core. However, the 40GBASE-KR4 variations of the

40-100GbE IP core have additional 40GBASE-KR4 related registers and register fields.

For your convenience, the 40-100GbE IP core user guide includes an appendix with the 10GBASE-KR

3-92

PRBS Registers

UG-01088

2014.12.15

Altera Corporation

Functional Description