Altera 40-Gbps Ethernet MAC and PHY MegaCore Function User Manual

Page 141

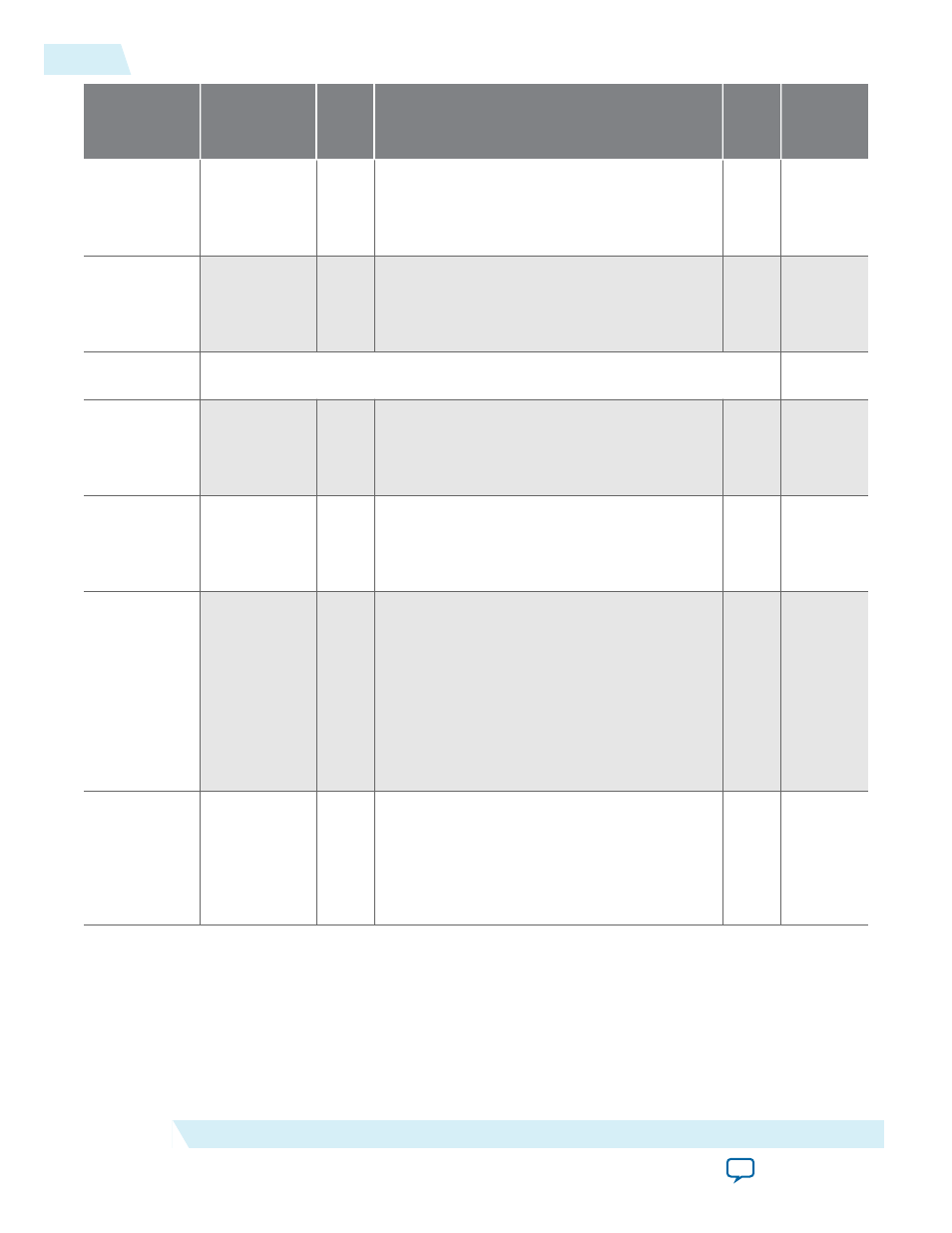

Address

Name

Bit

Description

HW

Reset

Value

Access

0x0B9

KR4 FEC

Corrected

Blocks, Lane

2

[31:0] Maintains count of corrected FEC blocks on

Lane 2, saturating (not rolling over) at 2

32

-1.

Resets to 0 when read. Refer to Clause 74.8.4.1 of

IEEE Std 802.3ap-2007.

32'b0 RO

0x0BA

KR4 FEC

Uncorrected

Blocks, Lane

2

[31:0] Maintains count of uncorrected (uncorrectable)

FEC blocks on Lane 2, saturating (not rolling

over) at 2

32

-1. Resets to 0 when read. Refer to

Clause 74.8.4.2 of IEEE Std 802.3ap-2007.

32'b0 RO

0x0BB

This register is the equivalent of register 0xB2 for Lane 3. (Refer to

).

RW

0x0BC

KR4 FEC

Corrected

Blocks, Lane

3

[31:0] Maintains count of corrected FEC blocks on

Lane 3, saturating (not rolling over) at 2

32

-1.

Resets to 0 when read. Refer to Clause 74.8.4.1 of

IEEE Std 802.3ap-2007.

32'b0 RO

0x0BD

KR4 FEC

Uncorrected

Blocks, Lane

3

[31:0] Maintains count of uncorrected FEC blocks on

Lane 3, saturating (not rolling over) at 2

32

-1.

Resets to 0 when read. Refer to Clause 74.8.4.2 of

IEEE Std 802.3ap-2007.

32'b0 RO

0x0C0

Override AN

Channel

Enable

[6]

Overrides the auto-negotiation master channel

that you set with the Auto-Negotiation Master

parameter, setting the new master channel

according to the value in register 0xCC[3:0].

While 0x0C0[6] has the value of 1, the channel

encoded in 0xCC[3:0] is the master channel.

While 0xC0[6] has the value of 0, the master

channel is the channel that you set with the

Auto-Negotiation Master parameter.

1'b0

RW

0x0CB

AN LP ADV

FEC_F[1:0]

[26:25

]

Received FEC ability bits. Bit [26] is FEC

requested and bit [25] is FEC ability. FEC

(F0:F1) is encoded in bits D46:D47 of the base

Link Codeword in Clause 73 AN. F0 is FEC

ability and F1 is FEC requested. Refer to Clause

73.6.5 of IEEE Std 802.3ap-2007.

2'b0

RO

3-94

40GBASE-KR4 Registers

UG-01088

2014.12.15

Altera Corporation

Functional Description