Altera 40-Gbps Ethernet MAC and PHY MegaCore Function User Manual

Page 124

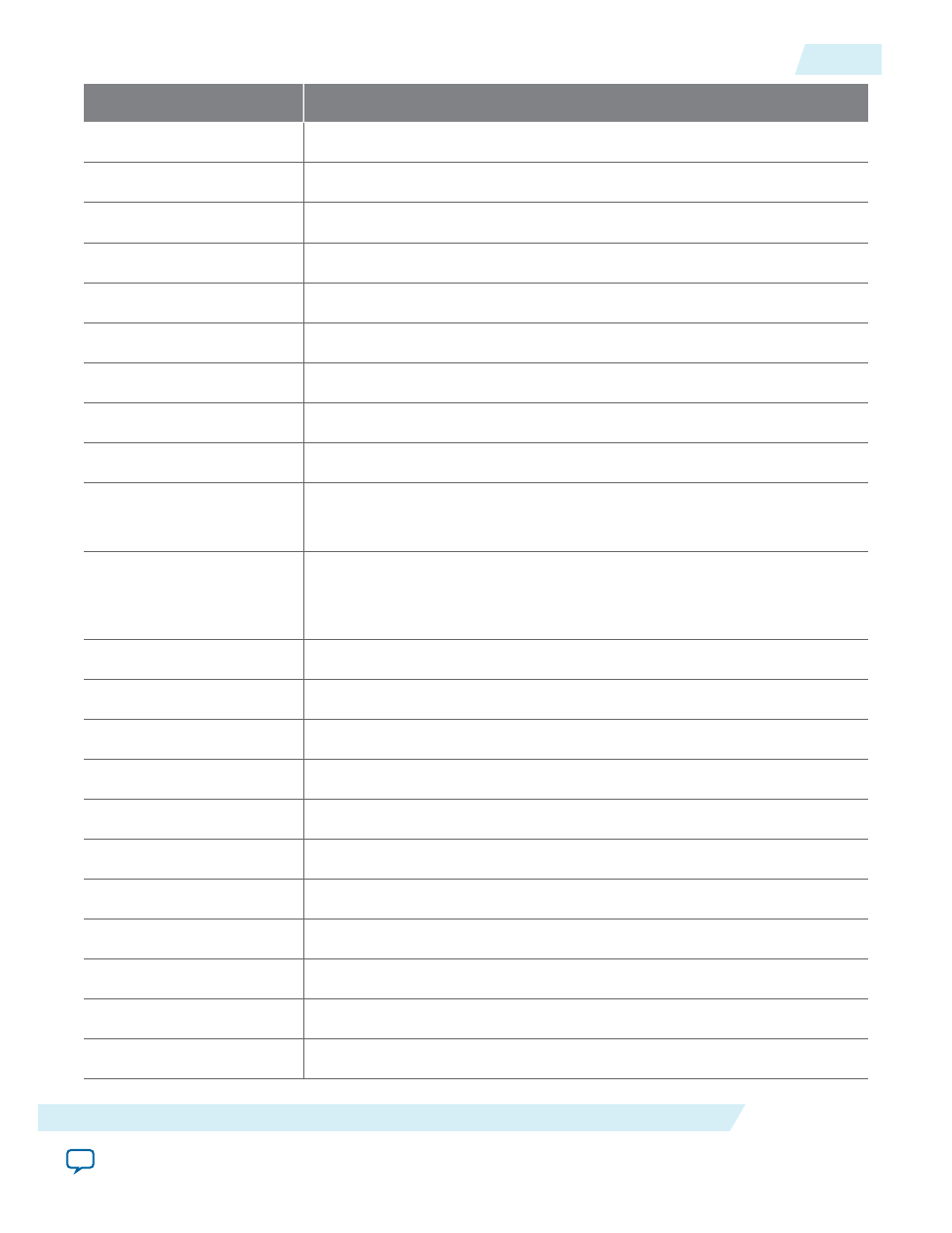

Word Offset

Register Description

0x01A

Test pattern counter register.

0x01B

One of two link fault signaling registers.

0x01C

Reserved.

0x01D

PHY reset register.

0x01E–0x01F

Reserved.

0x020–0x023

PCS-VLANE registers.

0x024–0x02F

Reserved.

0x030–0x032

PRBS registers.

0x033–0x03F

Reserved.

0x040–0x07F

(Stratix IV only)

Reserved.

0x040–0x07F

(Arria V GZ and Stratix V)

For all options except the CAUI-4 configuration: Maps to word addresses

0x040-0x07F in the Low Latency PHY IP core register map.

For the CAUI-4 configuration only : Reserved.

0x080–0x0FF

Reserved in non-40GBASE-KR4 IP core variations.

0x080–0x0AF

Reserved in 40GBASE-KR4 IP core variations.

0x0B0–0x0BD

40GBASE-KR4 top-level and FEC registers.

0x0BE–0x0BF

Reserved.

0x0C0–0x0CC

40GBASE-KR4 auto-negotiation registers.

0x0CD–0x0CF

Reserved.

0x0D0–0x0EB

40GBASE-KR4 link training registers.

0x0EC–0x0FF

Reserved.

0x100–0x103

MAC configuration and filter registers.

0x104–0x10F

Reserved.

0x110–0x117

Pause registers.

UG-01088

2014.12.15

Software Interface: Registers

3-77

Functional Description

Altera Corporation