Altera 40-Gbps Ethernet MAC and PHY MegaCore Function User Manual

Page 156

parameter in the 40-100GbE parameter editor, the counters are not implemented in the CSR, and read

access to the counters returns read data equal to 0.

To read the value of a statistics register without clearing it, write the value of 0x4 to the

MAC_CMD_config

register. To read the value of a statistics register and reset the counters, write the value of 0xC to the

MAC_CMD_config

register.

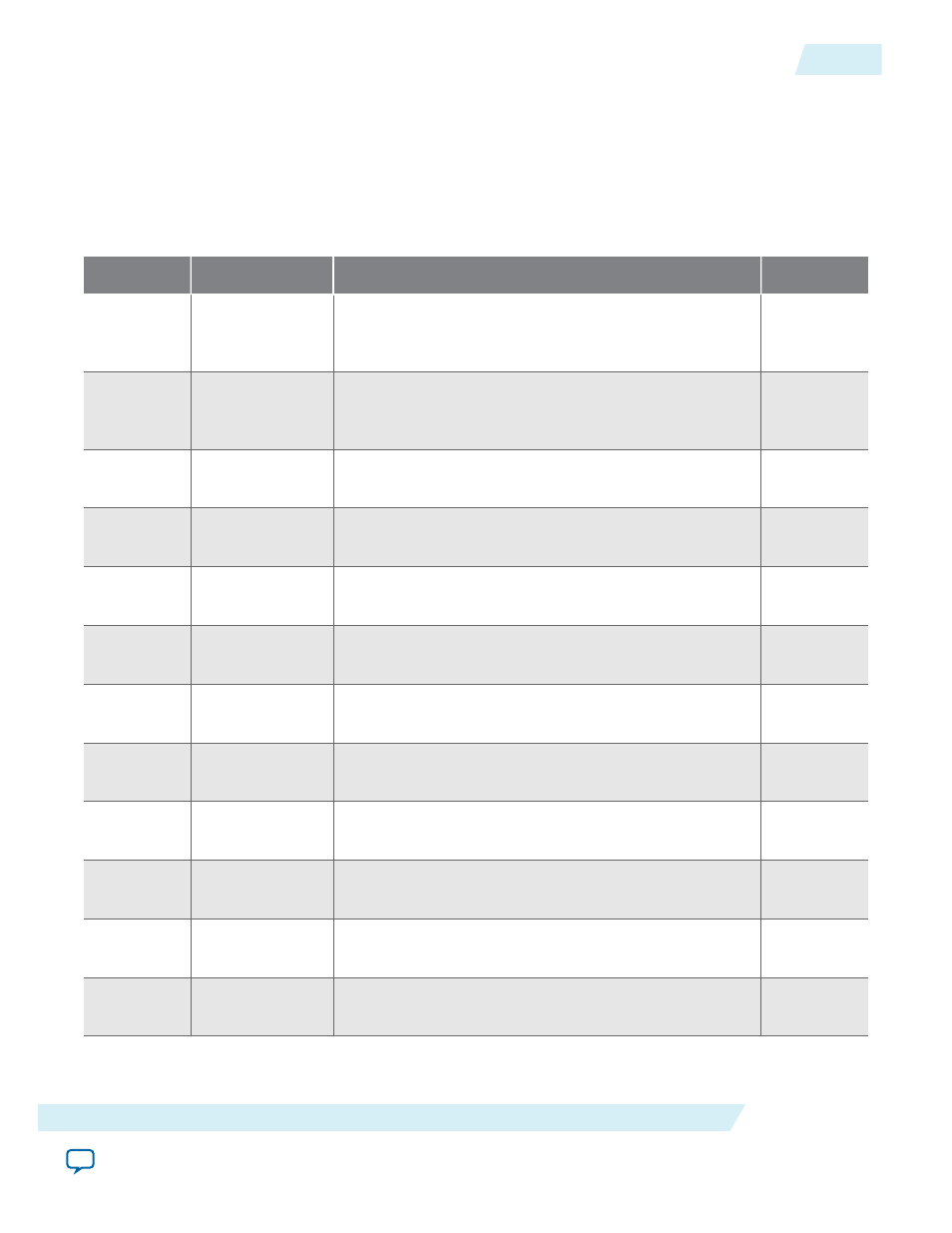

Table 3-48: Transmit Side Statistics Registers

The initial value after reset is 0 for all statistics registers.

Address

Name-

Description

Access

0x200

CNTR_TX_64B_LO

Number of 64-byte transmitted frames, including the CRC

field but excluding the preamble and SFD bytes (lower 32

bits)

RO

0x201

CNTR_TX_64B_HI

Number of 64-byte transmitted frames (upper 32 bits),

including the CRC field but excluding the preamble and SFD

bytes (upper 32 bits)

RO

0x202

CNTR_TX_

65to127B_LO

Number of transmitted frames between 65–127 bytes (lower

32 bits)

RO

0x203

CNTR_TX_

65to127B_HI

Number of transmitted frames between 65–127 bytes (upper

32 bits)

RO

0x204

CNTR_TX_

128to255B_LO

Number of transmitted frames between 128–255 bytes

(lower 32 bits)

RO

0x205

CNTR_TX_

128to255B_HI

Number of transmitted frames between 128–255 bytes

(upper 32 bits)

RO

0x206

CNTR_TX_

256to511B_LO

Number of transmitted frames between 256–511 bytes

(lower 32 bits)

RO

0x207

CNTR_TX_

256to511B_HI

Number of transmitted frames between 256–511 bytes

(upper 32 bits)

RO

0x208

CNTR_TX_

512to1023B_LO

Number of transmitted frames between 512–1023 bytes

(lower 32 bits)

RO

0x209

CNTR_TX_

512to1023B_HI

Number of transmitted frames between 512–1023 bytes

(upper 32 bits)

RO

0x20A

CNTR_TX_

1024to1518B_LO

Number of transmitted frames between 1024–1518 bytes

(lower 32 bits)

RO

0x20B

CNTR_TX_

1024to1518B_HI

Number of transmitted frames between 1024–1518 bytes

(upper 32 bits)

RO

UG-01088

2014.12.15

Statistics Registers

3-109

Functional Description

Altera Corporation