Resource utilization for 100gbe caui–4 ip cores – Altera 40-Gbps Ethernet MAC and PHY MegaCore Function User Manual

Page 19

Module

ALMs

Logic Registers

Memory

M9K

• • alt_e100_pcs_

tx:pcs_tx

11200

16600

0

• • alt_e100_phy_

csr:phy_csr

1100

1700

0

• alt_e100_phy_pma_

siv:pma

600

500

0

In the standard 100GbE variations, as in the 40GbE variations, some resource utilization numbers

decrease when statistics counters are not configured in the IP core. For example, compare the values for

the MAC with custom streaming client interface on a Stratix IV device with statistics counters included or

not included. When counters are included, the MAC requires 26600 ALMs, but when the counters are not

included, the MAC requires 23000 ALMs. The difference is 3600 ALMs. In a Stratix V device, the

difference is 2900 ALMs.

Related Information

Information about Quartus II resource utilization reporting, including ALMs needed.

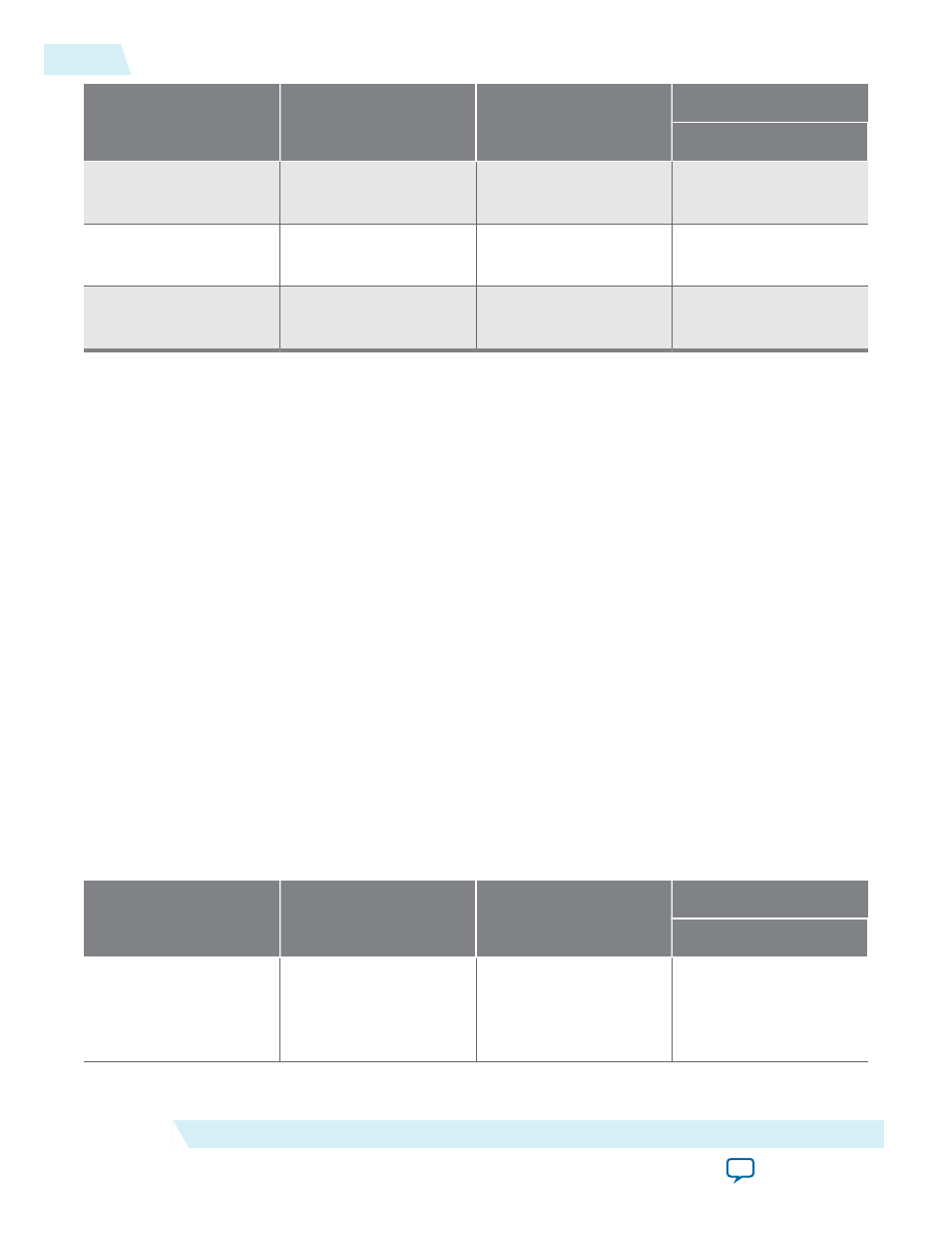

Resource Utilization for 100GbE CAUI–4 IP Cores

Resource utilization changes if the statistics counters are configured in the IP core. You can specify

whether to include or not include the statistics counters in the 40-100GbE parameter editor, but you

cannot change the setting dynamically.

Table 1-8: 100GbE CAUI–4 IP Core FPGA Resource Utilization

Lists the resources and expected performance for selected variations of the 100GbE CAUI-4 IP core with statistics

counters included or not included. The results were obtained using the Quartus II software v13.1 for a Stratix V

5SGTMC7K2F40C2 device.

• Top-level modules are in bold.

• The numbers of ALMs and logic registers are rounded up to the nearest 100.

• The numbers of ALMs, before rounding, are the ALMs needed numbers from the Quartus II Fitter Report.

Module

ALMs

Logic Registers

Memory

M20K

MAC&PHY with

Avalon-ST client

interface without

statistics counters

50100

102700

28

1-16

Resource Utilization for 100GbE CAUI–4 IP Cores

UG-01088

2014.12.15

Altera Corporation

About the 40- and 100-Gbps Ethernet MAC and PHY MegaCore Function