Avalon-mm mailbox registers – Altera Arria V Avalon-MM User Manual

Page 83

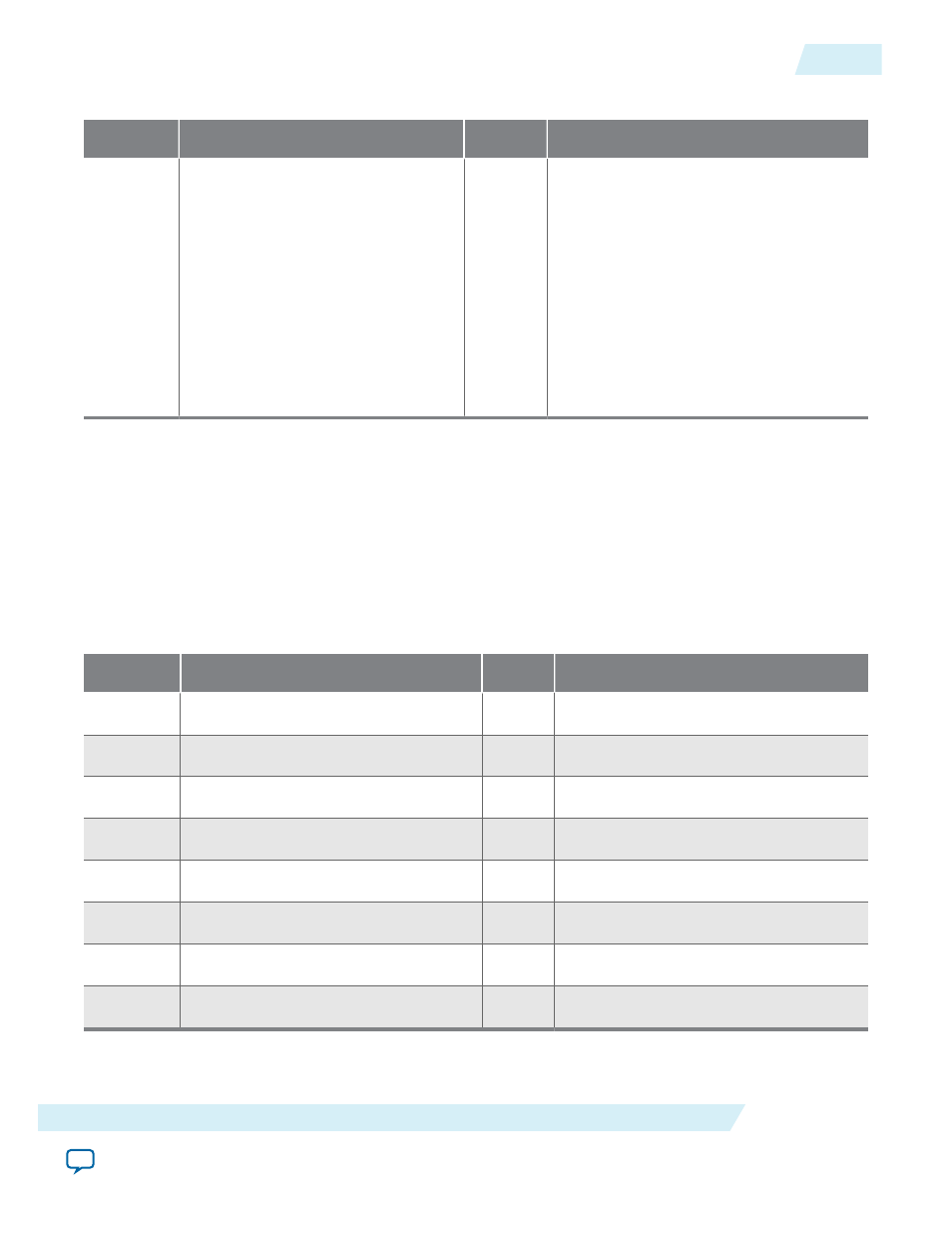

Table 5-20: INT‑X Interrupt Enable Register for Endpoints, 0x3070

Bits

Name

Access

Description

[31:0]

PCI Express to Avalon-MM

Interrupt Enable

RW

When set to 1, enables the interrupt for

the corresponding bit in the

PCI

Express to Avalon

MM Interrupt

Status

register to cause the Avalon

Interrupt signal (

cra_Irq_o

) to be

asserted.

Only bits implemented in the

PCI

Express to Avalon

MM Interrupt

Status

register are implemented in the

Enable register. Reserved bits cannot be

set to a 1.

Avalon-MM Mailbox Registers

A processor local to the interconnect fabric typically requires write access to a set of

Avalon-MM-to-PCI

Express Mailbox

registers and read-only access to a set of

PCI Express-to-Avalon-MM Mailbox

registers. Eight mailbox registers are available.

The

Avalon-MM-to-PCI Express Mailbox

registers are writable at the addresses shown in the following

table. When the Avalon-MM processor writes to one of these registers the corresponding bit in the

Avalon

MM to PCI Express Interrupt Status

register is set to 1.

Table 5-21: Avalon-MM to PCI Express Mailbox Registers, 0x3A00–0x3A1F

Address

Name

Access

Description

0x3A00

A2P_MAILBOX0

RW

Avalon-MM-to-PCI Express mailbox 0

0x3A04

A2P_MAILBOX1

RW

Avalon-MM-to-PCI Express mailbox 1

0x3A08

A2P _MAILBOX2

RW

Avalon-MM-to-PCI Express mailbox 2

0x3A0C

A2P _MAILBOX3

RW

Avalon-MM-to-PCI Express mailbox 3

0x3A10

A2P _MAILBOX4

RW

Avalon-MM-to-PCI Express mailbox 4

0x3A14

A2P _MAILBOX5

RW

Avalon-MM-to-PCI Express mailbox 5

0x3A18

A2P _MAILBOX6

RW

Avalon-MM-to-PCI Express mailbox 6

0x3A1C

A2P_MAILBOX7

RW

Avalon-MM-to-PCI Express mailbox 7

UG-01105_avmm

2014.12.15

Avalon-MM Mailbox Registers

5-21

Registers

Altera Corporation