Altera Arria V Avalon-MM User Manual

Page 41

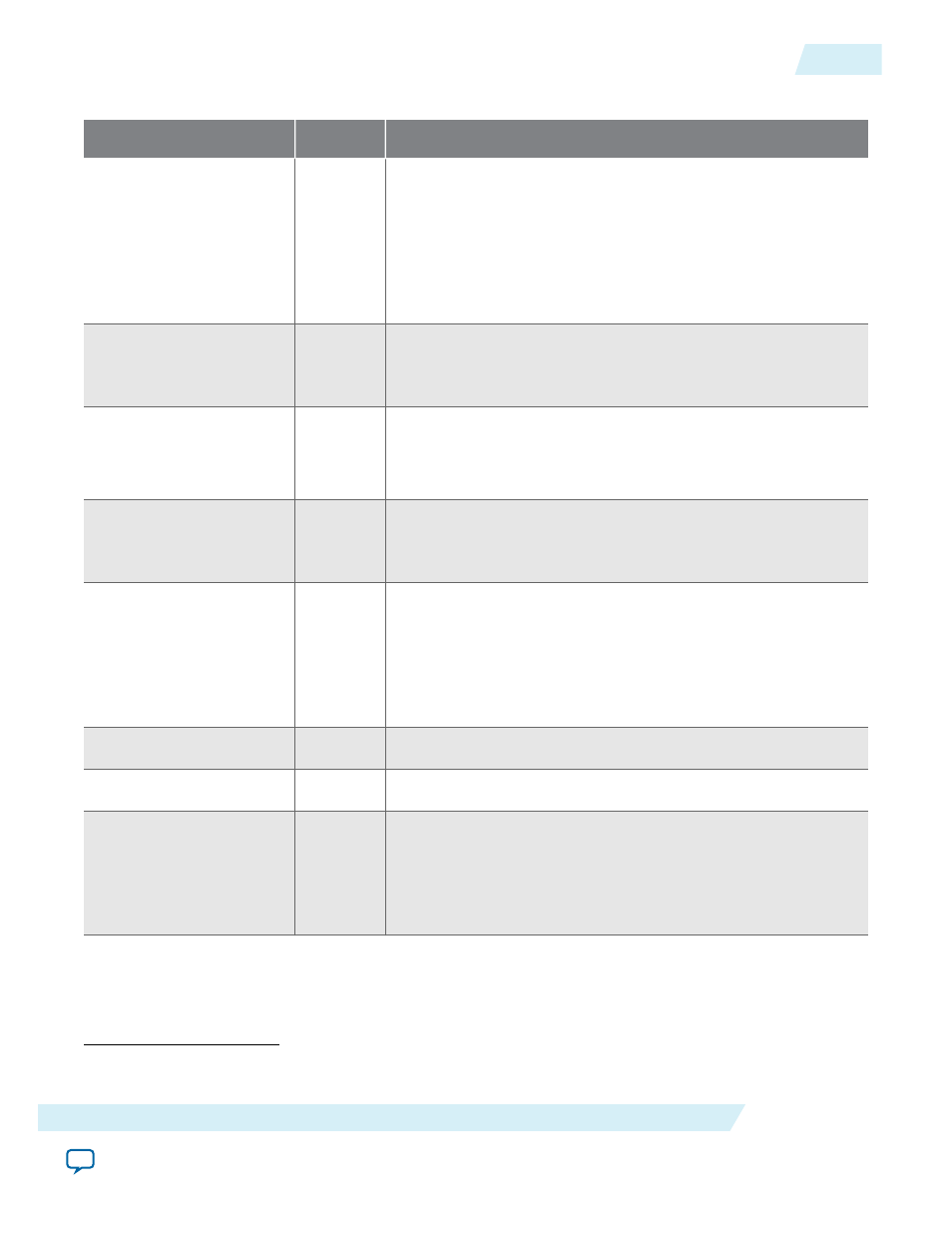

Table 4-6: Status and Link Training Signals

Signal

Direction

Description

derr_cor_ext_rcv

Output

Indicates a corrected error in the RX buffer. This signal is for

debug only. It is not valid until the RX buffer is filled with data.

This is a pulse, not a level, signal. Internally, the pulse is

generated with the 500 MHz clock. A pulse extender extends the

signal so that the FPGA fabric running at 250 MHz can capture

it. Because the error was corrected by the IP core, no Application

Layer intervention is required.

derr_cor_ext_rpl

Output

Indicates a corrected ECC error in the retry buffer. This signal is

for debug only. Because the error was corrected by the IP core,

no Application Layer intervention is required.

derr_rpl

Output

Indicates an uncorrectable error in the retry buffer. This signal is

for debug only.

The signal is not available for Arria V and Cyclone V devices.

dlup

Output

When asserted, indicates that the Hard IP block is in the Data

Link Control and Management State Machine (DLCMSM) DL_

Up state.

dlup_exit

Output

This signal is asserted low for one

pld_clk

cycle when the IP

core exits the DLCMSM DL_Up state, indicating that the Data

Link Layer has lost communication with the other end of the

PCIe link and left the Up state. When this pulse is asserted, the

Application Layer should generate an internal reset signal that is

asserted for at least 32 cycles.

ev128ns

Output

Asserted every 128 ns to create a time base aligned activity.

ev1us

Output

Asserted every 1µs to create a time base aligned activity.

hotrst_exit

Output

Hot reset exit. This signal is asserted for 1 clock cycle when the

LTSSM exits the hot reset state. This signal should cause the

Application Layer to be reset. This signal is active low. When this

pulse is asserted, the Application Layer should generate an

internal reset signal that is asserted for at least 32 cycles.

(3)

Debug signals are not rigorously verified and should only be used to observe behavior. Debug signals

should not be used to drive custom logic.

UG-01105_avmm

2014.12.15

Hard IP Status

4-11

Interfaces and Signal Descriptions

Altera Corporation