Avalon memory‑mapped system settings – Altera Arria V Avalon-MM User Manual

Page 28

Avalon Memory‑Mapped System Settings

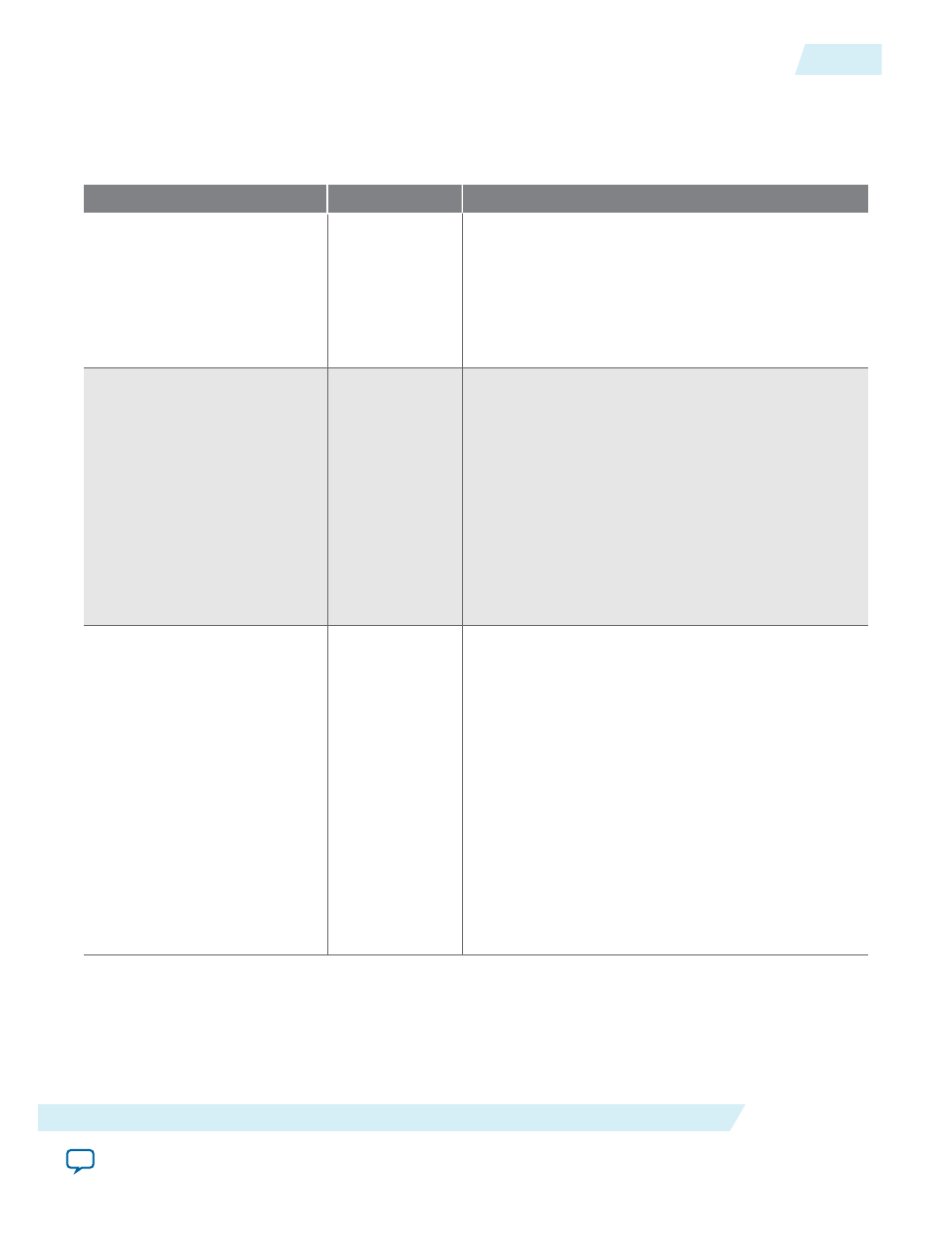

Table 3-9: Avalon Memory-Mapped System Settings

Parameter

Value

Description

Avalon-MM data width

64-bit

128-bit

Specifies the data width for the Application Layer to

Transaction Layer interface. Refer to Application

Layer Clock Frequencies for All Combinations of Link

Width, Data Rate and Application Layer Interface

Widths for all legal combinations of data width,

number of lanes, Application Layer clock frequency,

and data rate.

Avalon-MM address width

32-bit

64-bit

Specifies the address width for Avalon-MM RX

master ports that access Avalon-MM slaves in the

Avalon address domain. When you select 32-bit

addresses, the PCI Express Avalon-MM Bridge

performs address translation. When you specify 64-

bits addresses, no address translation is performed in

either direction. The destination address specified is

forwarded to the Avalon-MM interface without any

changes.

For the Avalon-MM interface with DMA, this value

must be set to 64.

Peripheral mode

Requester/

Completer

Completer-Only

Specifies whether the Avalon-MM Arria V Hard IP

for PCI Express is capable of sending requests to the

upstream PCI Express devices, and whether the

incoming requests are pipelined.

Requester/Completer—In this mode, the Hard IP

can send request packets on the PCI Express TX link

and receive request packets on the PCI Express RX

link.

Completer-Only—In this mode, the Hard IP can

receive requests, but cannot initiate upstream

requests. However, it can transmit completion packets

on the PCI Express TX link. This mode removes the

Avalon-MM TX slave port and thereby reduces logic

utilization.

UG-01105_avmm

2014.12.15

Avalon Memory‑Mapped System Settings

3-9

Parameter Settings

Altera Corporation