Pci express-to-avalon-mm read completions, Pci express-to-avalon-mm downstream write requests, Pci express-to-avalon-mm downstream read requests – Altera Arria V Avalon-MM User Manual

Page 128

PCI Express-to-Avalon-MM Read Completions

The PCI Express Avalon-MM bridge returns read completion packets to the initiating Avalon-MM

master in the issuing order. The bridge supports multiple and out-of-order completion packets.

PCI Express-to-Avalon-MM Downstream Write Requests

The PCI Express Avalon-MM bridge receives PCI Express write requests, it converts them to burst write

requests before sending them to the interconnect fabric. For Endpoints, the bridge translates the PCI

Express address to the Avalon-MM address space based on the BAR hit information and on address

translation table values configured during the IP core parameterization. For Root Ports, all requests are

forwarded to a single RX Avalon-MM master that drives them to the interconnect fabric. Malformed write

packets are dropped, and therefore do not appear on the Avalon-MM interface.

For downstream write and read requests, if more than one byte enable is asserted, the byte lanes must be

adjacent. In addition, the byte enables must be aligned to the size of the read or write request.

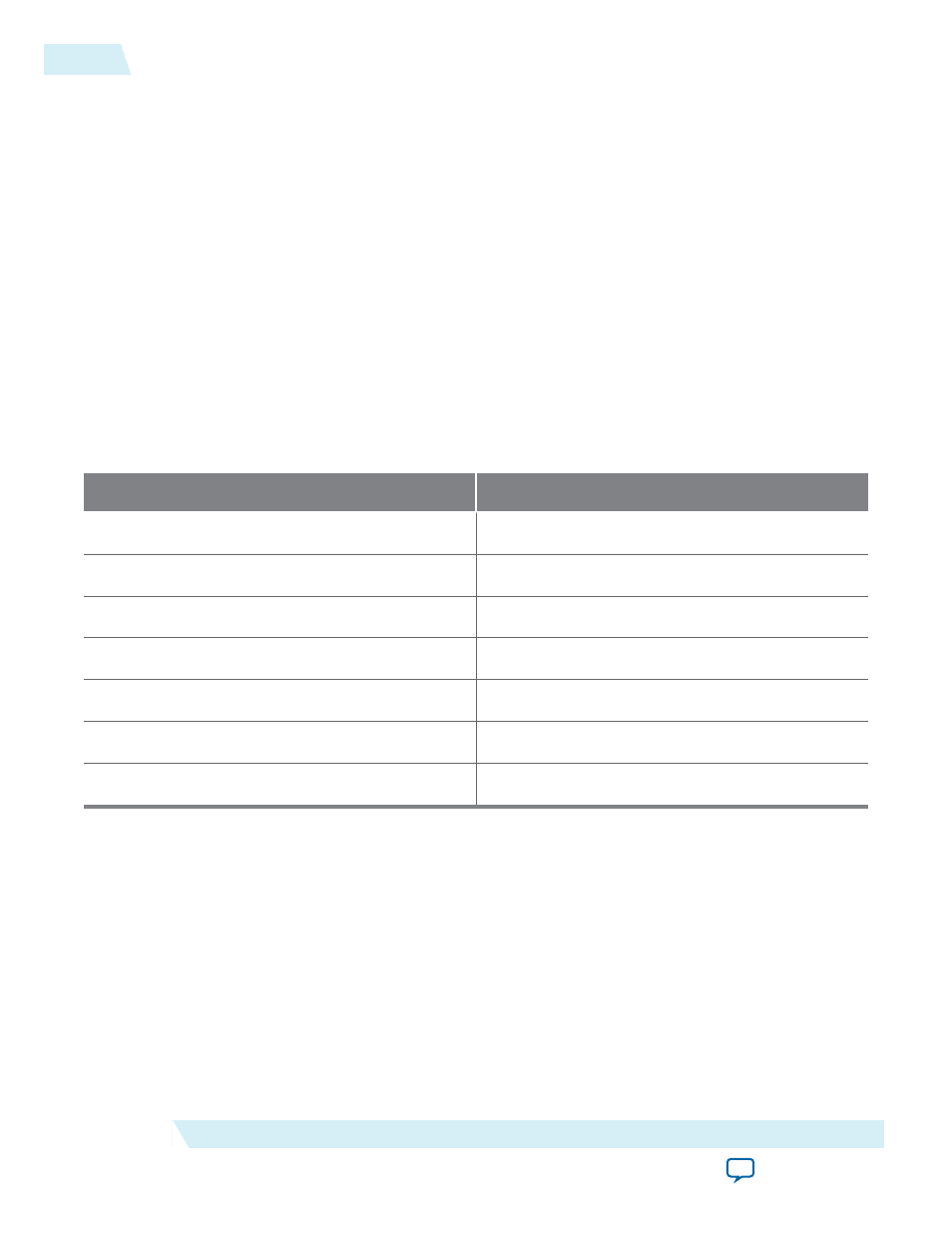

As an example, the following table lists the byte enables for 32-bit data.

Table 9-2: Valid Byte Enable Configurations

Byte Enable Value

Description

4’b1111

Write full 32 bits

4’b0011

Write the lower 2 bytes

4’b1100

Write the upper 2 bytes

4’b0001

Write byte 0 only

4’b0010

Write byte 1 only

4’b0100

Write byte 2 only

4’b1000

Write byte 3 only

In burst mode, the Arria V Hard IP for PCI Express supports only byte enable values that correspond to a

contiguous data burst. For the 32-bit data width example, valid values in the first data phase are 4’b1111,

4’b1110, 4’b1100, and 4’b1000, and valid values in the final data phase of the burst are 4’b1111, 4’b0111,

4’b0011, and 4’b0001. Intermediate data phases in the burst can only have byte enable value 4’b1111.

PCI Express-to-Avalon-MM Downstream Read Requests

The PCI Express Avalon-MM bridge sends PCI Express read packets to the interconnect fabric as burst

reads with a maximum burst size of 512 bytes. For Endpoints, the bridge converts the PCI Express address

to the Avalon-MM address space based on the BAR hit information and address translation lookup table

values. The RX Avalon-MM master port drives the received address to the fabric. You can set up the

Address Translation Table Configuration in the parameter editor. Unsupported read requests generate a

completer abort response.

9-12

PCI Express-to-Avalon-MM Read Completions

UG-01105_avmm

2014.12.15

Altera Corporation

IP Core Architecture