Altera Arria V Avalon-MM User Manual

Page 76

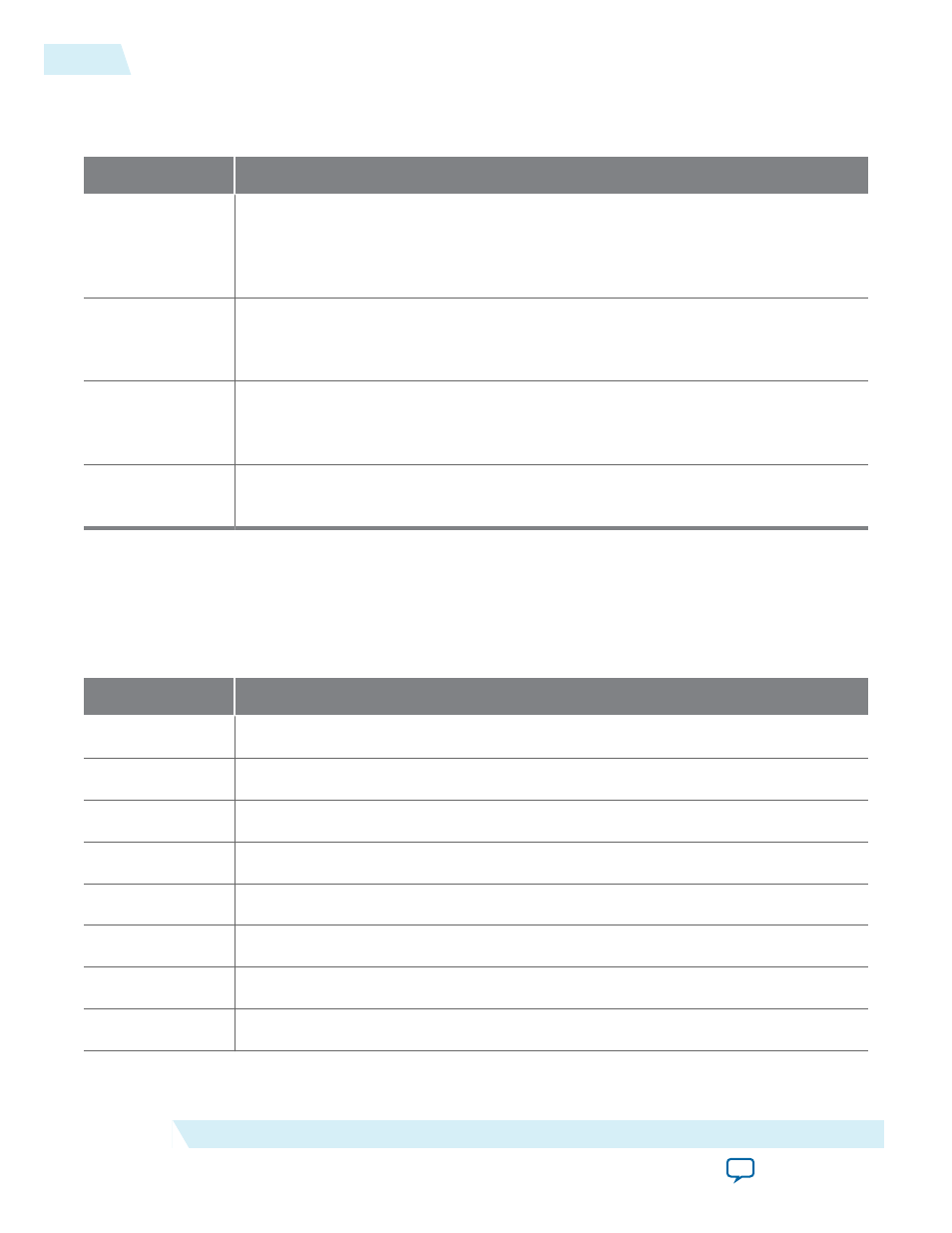

The following table describes the four subregions.

Table 5-11: Avalon-MM Control and Status Register Address Spaces

AddressRange

Address Space Usage

0x0000-0x0FFF Registers typically intended for access by PCI Express link partner only. This includes

PCI Express interrupt enable controls, write access to the PCI Express Avalon-MM

bridge mailbox registers, and read access to Avalon-MM-to-PCI Express mailbox

registers.

0x1000-0x1FFF Avalon-MM-to-PCI Express address translation tables. Depending on the system

design these may be accessed by the PCI Express link partner, Avalon-MM processors,

or both.

0x2000-0x2FFF Root Port request registers. An embedded processor, such as the Nios II processor,

programs these registers to send the data for Configuration TLPs, I/O TLPs, single

dword Memory Read and Write requests, and receive interrupts from an Endpoint.

0x3000-0x3FFF Registers typically intended for access by Avalon-MM processors only. Provides host

access to selected Configuration Space and status registers.

Note: The data returned for a read issued to any undefined address in this range is unpredictable.

The following table lists the complete address map for the PCI Express Avalon-MM bridge registers.

Note: In the following table the text in green are links to the detailed register description

Table 5-12: PCI Express Avalon-MM Bridge Register Map

Address Range

Register

0x0040

Avalon-MM to PCI Express Interrupt Status Register

0x0050

Avalon-MM to PCI Express Interrupt Status Enable Register

0x0800–0x081F PCI Express-to-Avalon-MM Mailbox Registers

0x0900–x091F

Avalon-MM to PCI Express Mailbox Registers

0x1000–0x1FFF Avalon-MM to PCI Express Address Translation Table

0x2000–0x2FFF Root Port TLP Data Registers

0x3060

Avalon-MM to PCI Express Interrupt Status Registers for Root Ports

0x3060

PCI Express to Avalon-MM Interrupt Status Register for Endpoints

5-14

64- or 128-Bit Avalon-MM Bridge Register Descriptions

UG-01105_avmm

2014.12.15

Altera Corporation

Registers