Altera Arria V Avalon-MM User Manual

Page 44

Signal

Direction

Description

MsiControl_o[15:0]

Output

Provides for system software control of MSI as defined in Section

6.8.1.3 Message Control for MSI in the PCI Local Bus Specifica‐

tion, Rev. 3.0. The following fields are defined:

•

MsiControl_o[15:9]

: Reserved

•

MsiControl_o[8]

: Per-vector masking capable

•

MsiControl_o[7]

: 64-bit address capable

•

MsiControl_o[6:4]

: Multiple Message Enable

•

MsiControl_o[3:1]

: MSI Message Capable

•

MsiControl_o[0]

: MSI Enable.

MsixIntfc_o[15:0]

Output

Provides for system software control of MSI-X as defined in

Section 6.8.2.3 Message Control for MSI-X in the PCI Local Bus

Specification, Rev. 3.0. The following fields are defined:

•

MsixIntfc_o[15]

: Enable

•

MsixIntfc_o[14]

: Mask

•

MsixIntfc_o[13:11]

: Reserved

•

MsixIntfc_o[10:0]

: Table size

IntxReq_i

Input

When asserted, the Endpoint is requesting attention from the

interrupt service routine unless MSI or MSI-X interrupts are

enabled. Remains asserted until the device driver clears the

pending request.

IntxAck_o

Output

This signal is the acknowledge for

IntxReq_i

. It is asserted for at

least one cycle either when either of the following events occur:

• The

Assert_INTA

message TLP has been transmitted in

response to the assertion of the

IntxReq_i

.

• The

Deassert_INTA

message TLP has been transmitted in

response to the deassertion of the

IntxReq_i

signal.

Refer to the timing diagrams below.

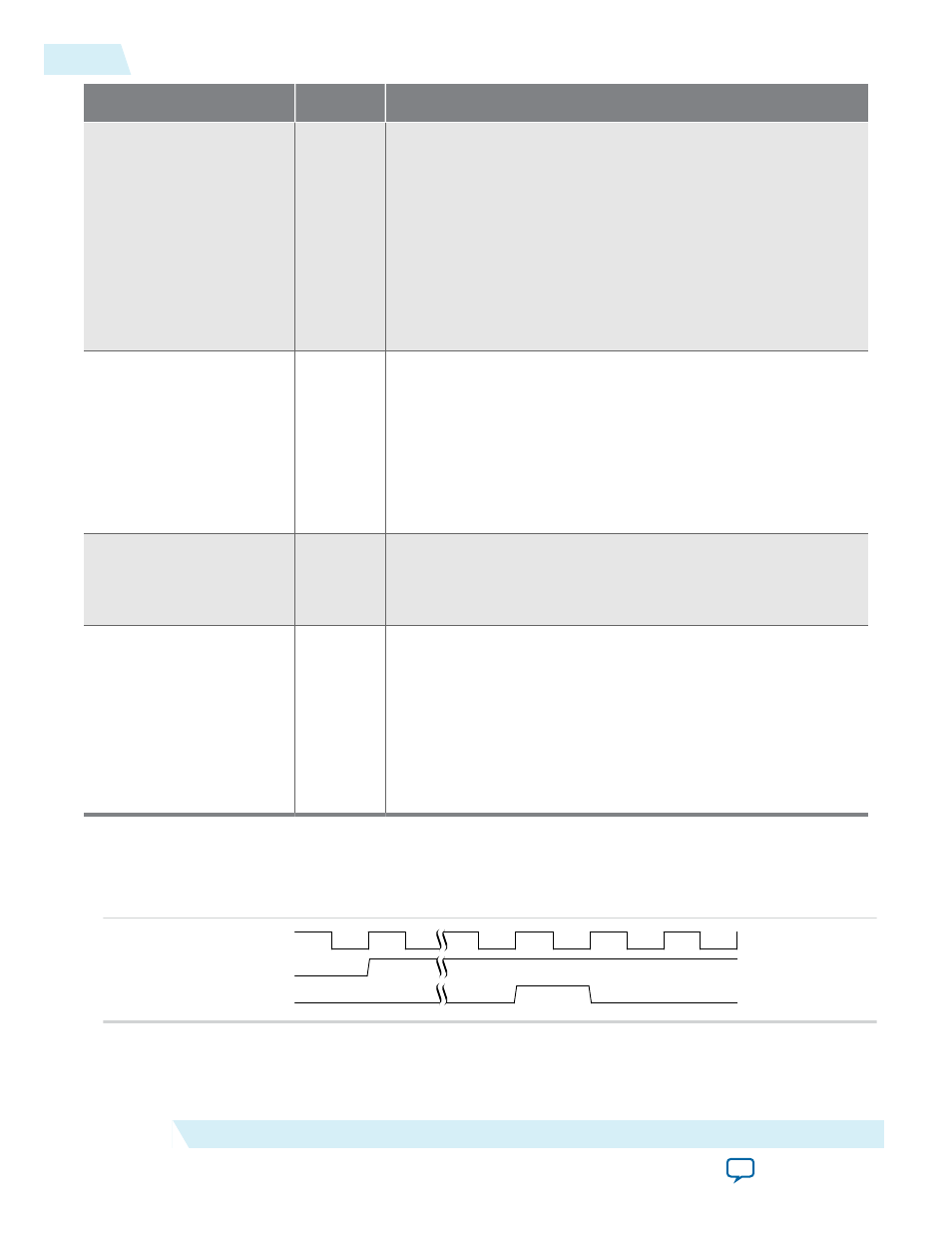

The following figure illustrates interrupt timing for the legacy interface. In this figure the assertion of

IntxReq_i

instructs the Hard IP for PCI Express to send an

Assert_INTA

message TLP.

Figure 4-3: Legacy Interrupt Assertion

clk

IntxReq_i

IntAck_o

The following figure illustrates the timing for deassertion of legacy interrupts. The assertion of

IntxReq_i

instructs the Hard IP for PCI Express to send a

Deassert_INTA

message.

4-14

Interrupts for Endpoints when Multiple MSI/MSI‑X Support Is Enabled

UG-01105_avmm

2014.12.15

Altera Corporation

Interfaces and Signal Descriptions