Figure 9-4: pci express avalon-mm bridge, Pci express megacore function tx slave module, Pci link cra slave module – Altera Arria V Avalon-MM User Manual

Page 126

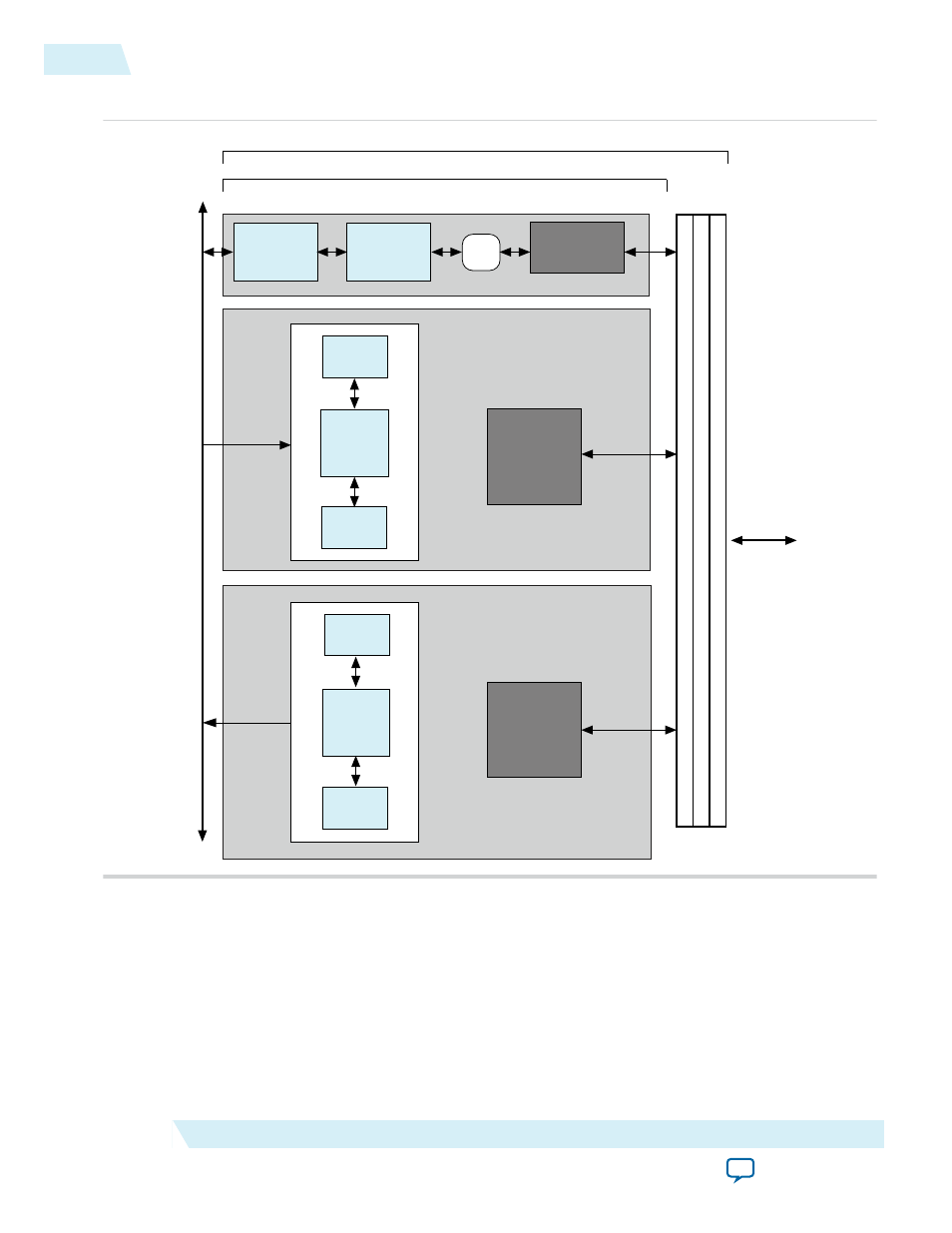

Figure 9-4: PCI Express Avalon-MM Bridge

Transac

tion L

ay

er

PCI Express

Tx Controller

PCI Express

Rx Controller

Da

ta Link L

ay

er

Ph

ysic

al L

ay

er

PCI Express MegaCore Function

TX Slave Module

Control & Status

Reg (CSR)

Sync

Avalon Clock Domain

PCI Express Clock Domain

Rx Master Module

RX Master Module

PCI Express Avalon-MM Bridge

Sy

st

em Int

er

connec

t F

abric

PCI Link

CRA Slave Module

Address

Translator

Avalon-MM

Tx Read

Response

Avalon-MM

Tx Slave

Avalon-MM

Rx Read

Response

Avalon-MM

Rx Master

MSI or

Legacy Interrupt

Generator

Control Register

Access Slave

Address

Translator

The bridge has the following additional characteristics:

• Type 0 and Type 1 vendor-defined incoming messages are discarded

• Completion-to-a-flush request is generated, but not propagated to the interconnect fabric

For End Points, each PCI Express base address register (BAR) in the Transaction Layer maps to a specific,

fixed Avalon-MM address range. You can use separate BARs to map to various Avalon-MM slaves

connected to the RX Master port. In contrast to Endpoints, Root Ports do not perform any BAR matching

and forwards the address to a single RX Avalon-MM master port.

9-10

32-Bit PCI Express Avalon-MM Bridge

UG-01105_avmm

2014.12.15

Altera Corporation

IP Core Architecture