Altera Arria V Avalon-MM User Manual

Page 29

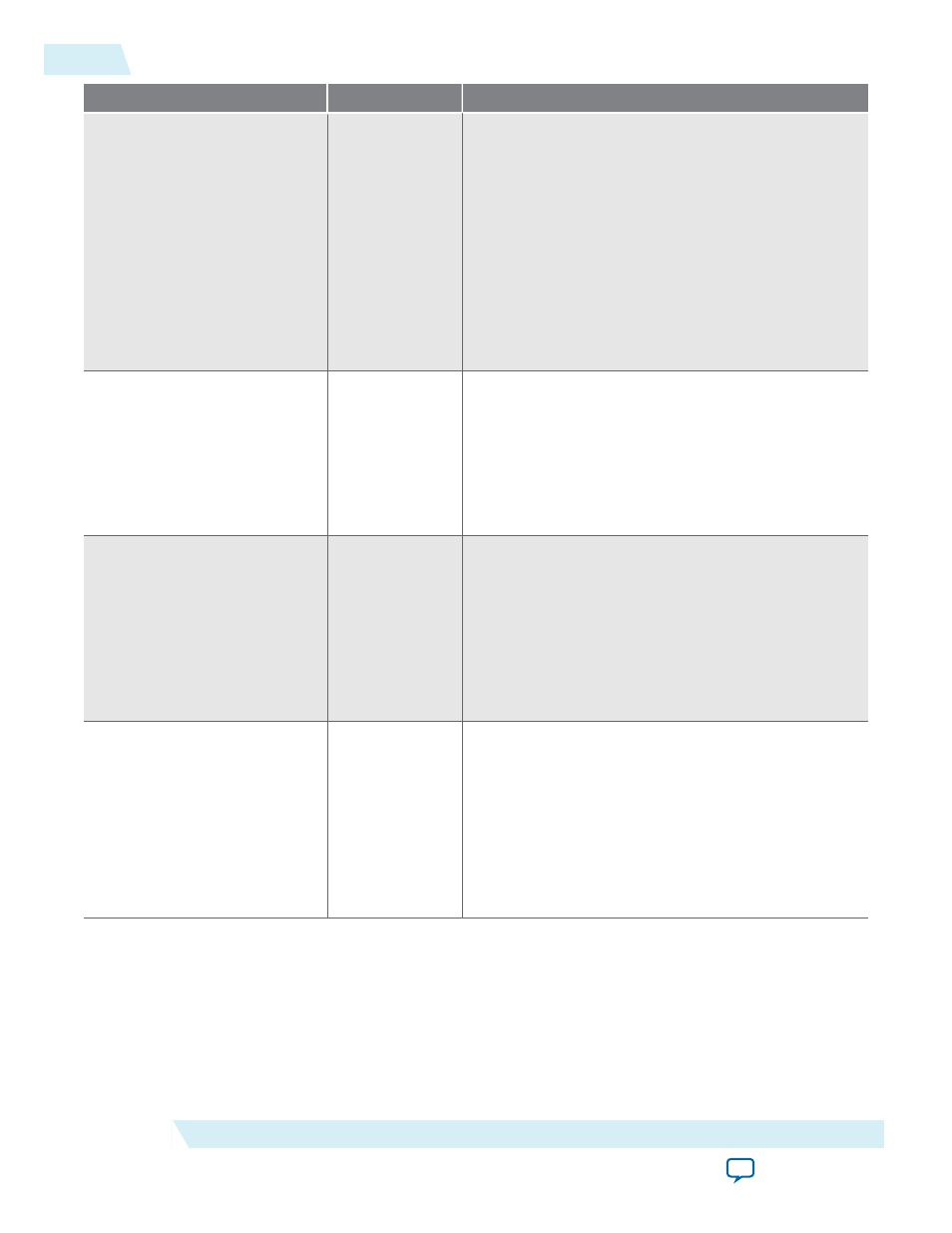

Parameter

Value

Description

Single DW Completer

On/Off

This is a non-pipelined version of Completer Only

mode. At any time, only a single request can be

outstanding. Single dword completer uses fewer

resources than Completer Only. This variant is

targeted for systems that require simple read and

write register accesses from a host CPU. If you select

this option, the width of the data for RXM BAR

masters is always 32 bits, regardless of the Avalon-

MM width.

For the Avalon-MM interface with DMA, this value

must be Off .

Control register access

(CRA) Avalon-MM slave

port

On/Off

Allows read and write access to bridge registers from

the interconnect fabric using a specialized slave port.

This option is required for Requester/Completer

variants and optional for Completer Only variants.

Enabling this option allows read and write access to

bridge registers, except in the Completer-Only single

dword variations.

Enable multiple MSI/MSI-X

support

On/Off

When you turn this option On, the core exports

top-level MSI and MSI-X interfaces that you can use

to implement a Customer Interrupt Handler for MSI

and MSI-X interrupts. For more information about

the Custom Interrupt Handler, refer to Interrupts for

End Points Using the Avalon-MM Interface with

Multiple MSI/MSI

-

X Support. If you turn this option

Off, the core handles interrupts internally.

Auto enabled PCIe interrupt

(enabled at power-on)

On/Off

Turning on this option enables the Avalon-MM

Arria V Hard IP for PCI Express interrupt register at

power-up. Turning off this option disables the

interrupt register at power-up. The setting does not

affect run-time configuration of the interrupt enable

register.

For the Avalon-MM interface with DMA, this value

must be Off.

3-10

Avalon Memory‑Mapped System Settings

UG-01105_avmm

2014.12.15

Altera Corporation

Parameter Settings