Rx block, Avalon-mm rx master block – Altera Arria V Avalon-MM User Manual

Page 136

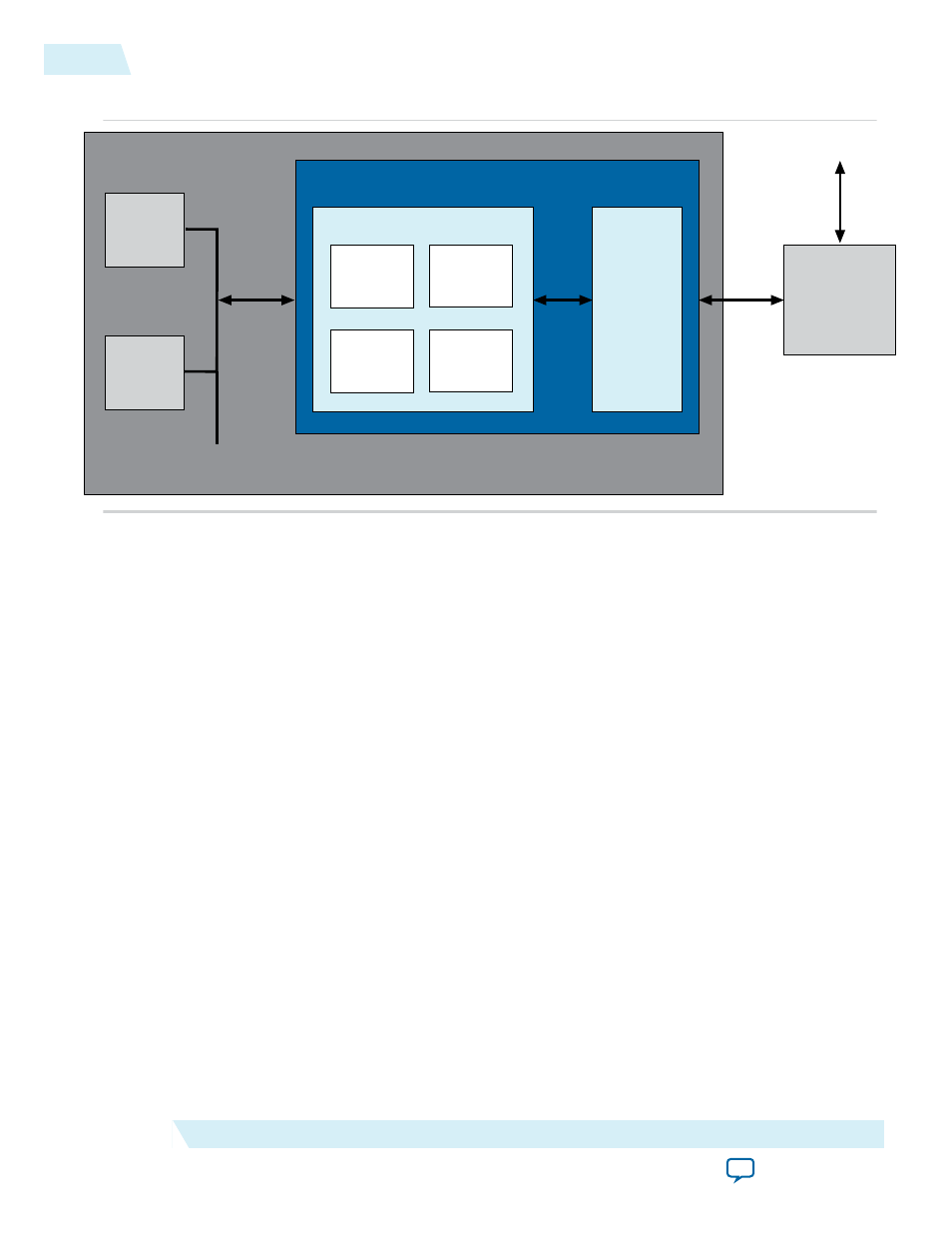

Figure 9-11: Qsys Design Including Completer Only Single Dword Endpoint for PCI Express

Qsys System

PCI Express

Root Complex

PCIe Link

to Host

CPU

Avalon-MM

Interconnect

Fabric

Avalon-MM

Slave

Avalon-MM

Slave

Avalon-MM

Hard IP

for PCIe

Avalon-MM

Master RX

Interrupt

Handler

RX Block

TX Block

Completer Only Single DWord Endpoint

Qsys Component

.

.

.

Bridge

The above figure shows the that completer-only single dword endpoint connects to a PCI Express root

complex. A bridge component includes the Arria V Hard IP for PCI Express TX and RX blocks, an

Avalon-MM RX master, and an interrupt handler. The bridge connects to the FPGA fabric using an

Avalon-MM interface. The following sections provide an overview of each block in the bridge.

RX Block

The RX Block control logic interfaces to the hard IP block to process requests from the root complex. It

supports memory reads and writes of a single dword. It generates a completion with Completer Abort

(CA) status for read requests greater than four bytes and discards all write data without further action for

write requests greater than four bytes.

The RX block passes header information to the Avalon-MM master, which generates the corresponding

transaction to the Avalon-MM interface. The bridge accepts no additional requests while a request is

being processed. While processing a read request, the RX block deasserts the

ready

signal until the TX

block sends the corresponding completion packet to the hard IP block. While processing a write request,

the RX block sends the request to the Avalon-MM interconnect fabric before accepting the next request.

Avalon-MM RX Master Block

The 32-bit Avalon-MM master connects to the Avalon-MM interconnect fabric. It drives read and write

requests to the connected Avalon-MM slaves, performing the required address translation. The RX master

supports all legal combinations of byte enables for both read and write requests.

For more information about legal combinations of byte enables, refer to Avalon Memory Mapped

Interfaces in the Avalon Interface Specifications.

Related Information

9-20

RX Block

UG-01105_avmm

2014.12.15

Altera Corporation

IP Core Architecture