Recommended speed grades – Altera Arria V Avalon-MM User Manual

Page 10

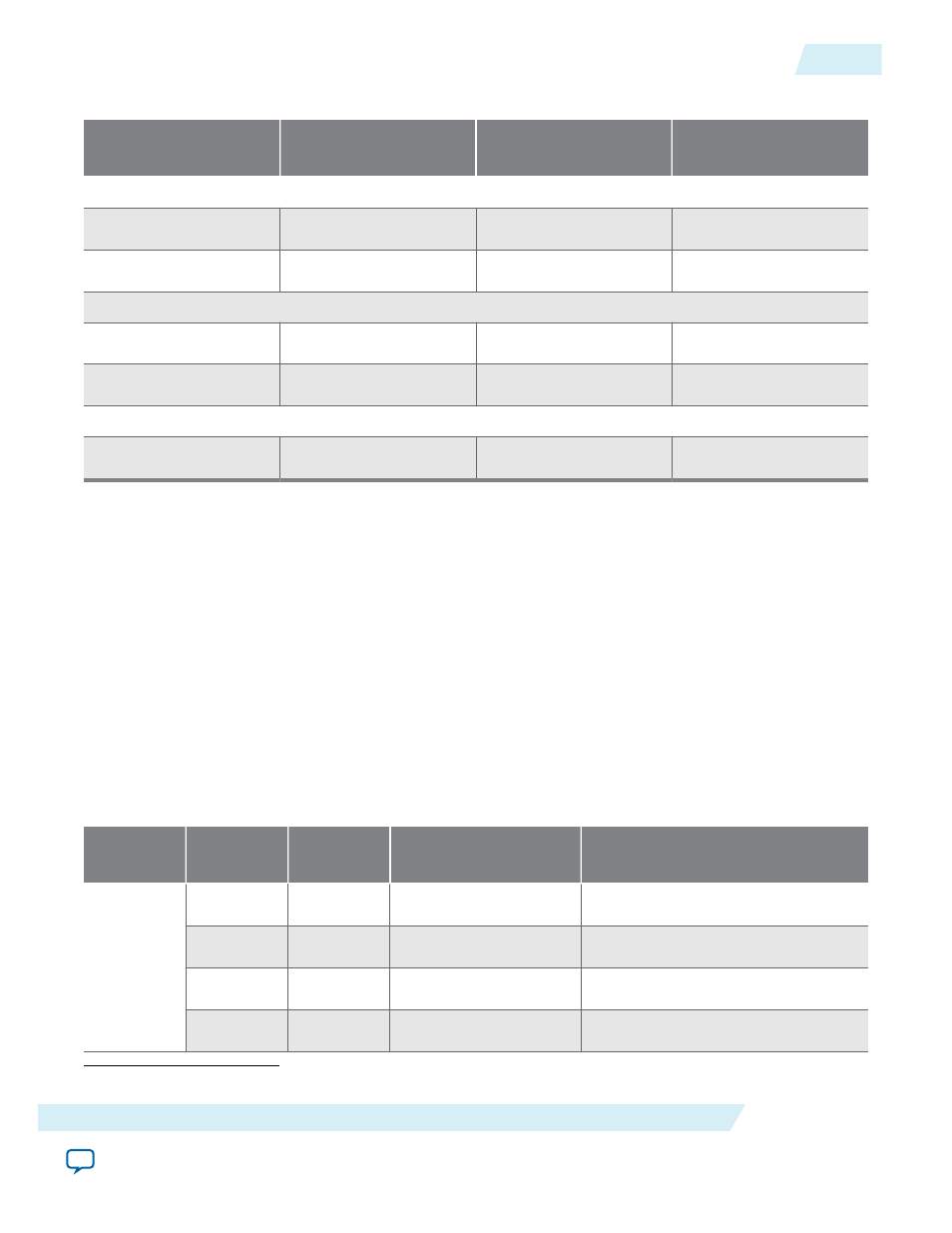

Table 1-5: Performance and Resource Utilization Avalon-MM Hard IP for PCI Express

Data Rate or Interface

Width

ALMs

Memory M10K

Logic Registers

Avalon-MM Bridge

Gen1 ×4

1250

27

1700

Gen2 ×8

2100

35

3050

Avalon-MM Interface–Completer Only

64

600

11

900

128

1350

22

2300

Avalon-MM–Completer Only Single DWord

64

160

0

230

Note: Soft calibration of the transceiver module requires additional logic. The amount of logic required

depends on the configuration.

Related Information

Recommended Speed Grades

Table 1-6: Arria V Recommended Speed Grades for Link Widths and Application Layer Clock Frequencies

Altera recommends setting the Quartus II Analysis & Synthesis Settings Optimization Technique to Speed when

the Application Layer clock frequency is 250 MHz. For information about optimizing synthesis, refer to Setting Up

and Running Analysis and Synthesis in Quartus II Help. For more information about how to effect the

Optimization Technique settings, refer to Area and Timing Optimization in volume 2 of the Quartus II

Handbook. .

Link Rate

Link Width

Interface

Width

Application Clock

Frequency (MHz)

Recommended Speed Grades

Gen1

×1

64 bits

62.5

(2)

,125

–4,–5,–6

×2

64 bits

125

–4,–5,–6

×4

64 bits

125

–4,–5,–6

×8

128 bits

125

–4,–5,–6

(2)

This is a power-saving mode of operation

UG-01105_avmm

2014.12.15

Recommended Speed Grades

1-9

Datasheet

Altera Corporation