Avalon interface specifications – Altera Arria V Avalon-MM User Manual

Page 32

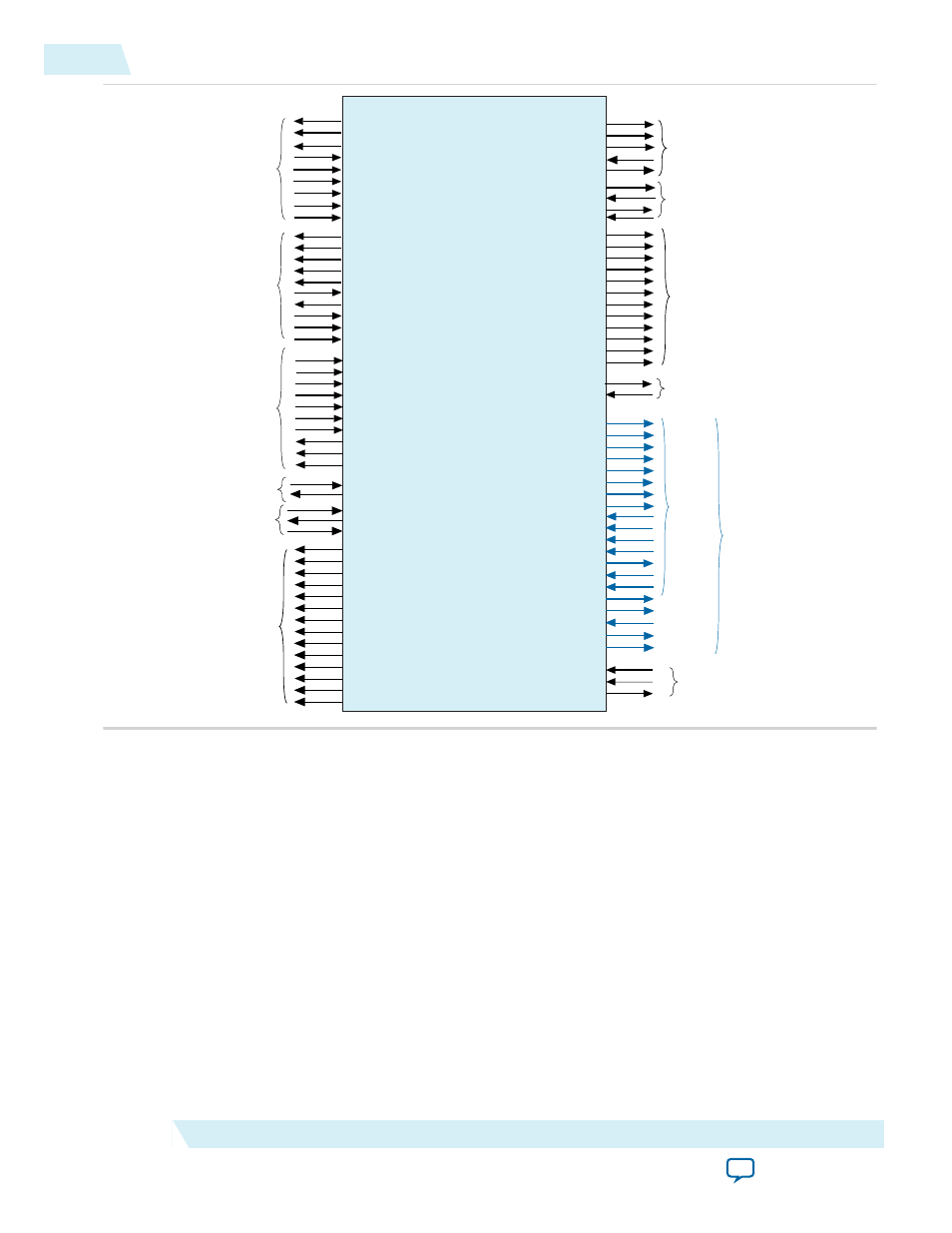

tx_out0[

rx_in0[

1-Bit Serial

CraReadData_o[31:0]

CraWaitRequest_o

CraByteEnable_i[3:0]

CraChipSelect_i

CraAddress_i[13:0]

CraRead_i

CraWrite_i

CraWriteData_i[31:0]

TxsWriteData_i[

TxsBurstCount_i[6 or 5:0]

TxsChipSelect_i

TxsRead_i

TxsWrite_i

TxsAddress_i[

TxsByteEnable_i[

TxsReadDataValid_o

TxsReadData_o[

TxsWaitRequest_o

32-Bit

Avalon-MM

CRA

Slave Port

(Optional)

64- or 128-Bit

Avalon-MM TX

Slave Port

64- or 128-Bit Avalon-MM Interface to Application Layer

Test

test_in[31:0]

simu_mode_pipe

hip_currentspeed[1:0]

RxmWrite_

RxmAddress_

RxmWriteData_

RxmByteEnable_

RxmBurstCount_

RxmWaitRequest_

RxmRead_

RxmReadData_i[

-1:0]

RxmReadDataValid_i

RxmIrq[

64-Bit

Avalon-MM RX BAR

Master Port

reconfig_fromxcvr[

reconfig_toxcvr[

busy_xcvr_reconfig

reconfig_clk_locked

Transceiver

Reconfiguration

txdatak0

txdata0[7:0]

txdetectrx0

txelectidle0

rxpolarity0

txcompl0

powerdown0[1:0]

tx_deemph0

rxdatak0

rxdata0[7:0]

rxvalid0

phystatus0

eidleinfersel0[2:0]

rxelectidle0

rxstatus0[2:0]

sim_ltssmstate[4:0]

sim_pipe_rate0[1:0]

sim_pipe_pclk_in

txswing0

txmargin0[2:0]

PIPE Interface

Simulation Only

8-Bit PIPE

Clocks

npor

nreset_status

pin_perstn

Reset

refclk

coreclkout

CraIrq_o

MsiIntfc_o[81:0]

MsiControl_o[15:0]

MsixIntfc_o[15:0]

IntxReq_i

IntxAck_o

Multiple

MSI/MSI-X

derr_cor_ext_rcv

derr_ext_rpl

derr_rpl

dlup

dlup_exit

ev128ns

ev1us

hotrst_exit

int_status[3:0]

ko_cpl_spc_data[11:0]

ko_cpl_spc_header[7:0]

l2_ext

lane_act[3:0]

ltssmstate[4:0]

Hard IP

Status

Hard IP

Status

Extension

pld_clk_inuse

pme_to_sr

rx_st_bar[7:0]

rx_st_data[127:0]

rx_st_eop

rx_st_err

rx_st_sop

rx_st_valid

serr_out

tl_cfg_add[3:0]

tx_cfg_sts[52:0]

tx_st_ready

Note: Signals listed for BAR0 are the same as those for BAR1–BAR5 when those BARs are enabled in the

parameter editor.

Variations using the Avalon-MM interface implement the Avalon-MM protocol described in the Avalon

Interface Specifications. Refer to this specification for information about the Avalon-MM protocol,

including timing diagrams.

Related Information

32-Bit Non-Bursting Avalon-MM Control Register Access (CRA) Slave Signals

The optional CRA port for the full-featured IP core allows upstream PCI Express devices and external

Avalon-MM masters to access internal control and status registers.

4-2

32-Bit Non-Bursting Avalon-MM Control Register Access (CRA) Slave Signals

UG-01105_avmm

2014.12.15

Altera Corporation

Interfaces and Signal Descriptions