Altera Arria V Avalon-MM User Manual

Page 61

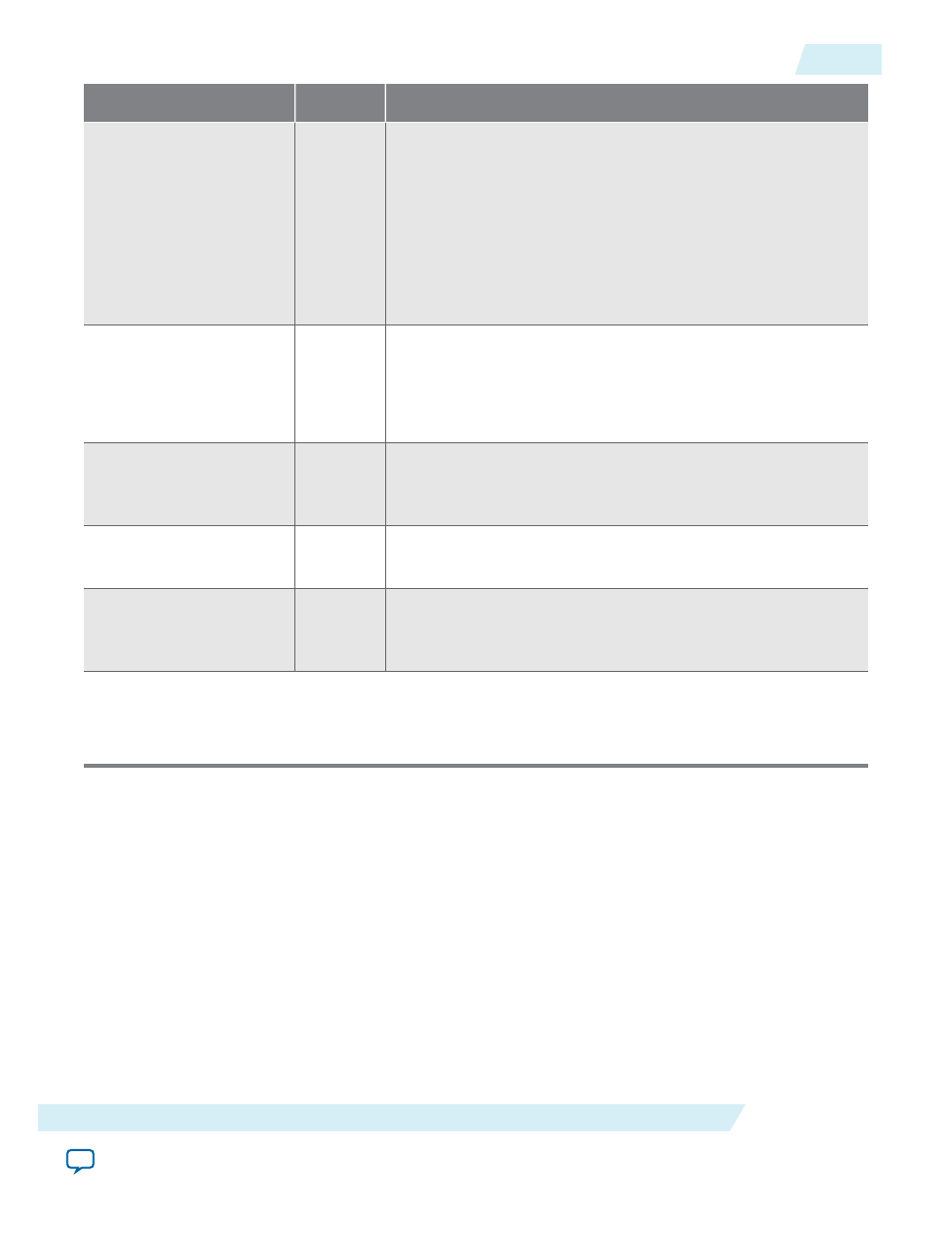

Signal

Direction

Description

• 5’b10101: LOs

• 5’b11001: L2.transmit.Wake

• 5’b11010: Speed.Recovery

• 5’b11011: Recovery.Equalization, Phase 0

• 5’b11100: Recovery.Equalization, Phase 1

• 5’b11101: Recovery.Equalization, Phase 2

• 5’b11110: Recovery.Equalization, Phase 3

• 5’b11111: Recovery.Equalization, Done

sim_pipe_rate[1:0]

Output

The 2-bit encodings have the following meanings:

• 2’b00: Gen1 rate (2.5 Gbps)

• 2’b01: Gen2 rate (5.0 Gbps)

• 2’b1X: Gen3 rate (8.0 Gbps)

sim_pipe_pclk_in

Input

This clock is used for PIPE simulation only, and is derived from

the

refclk

. It is the PIPE interface clock used for PIPE mode

simulation.

txswing0

Output

When asserted, indicates full swing for the transmitter voltage.

When deasserted indicates half swing.

tx_margin0[2:0]

Output

Transmit V

OD

margin selection. The value for this signal is based

on the value from the

Link Control 2

Register

. Available for

simulation only.

Notes:

1. These signals are for simulation only. For Quartus II software compilation, these pipe signals can be

left floating.

UG-01105_avmm

2014.12.15

PIPE Interface Signals

4-31

Interfaces and Signal Descriptions

Altera Corporation