Altera Arria V Avalon-MM User Manual

Page 49

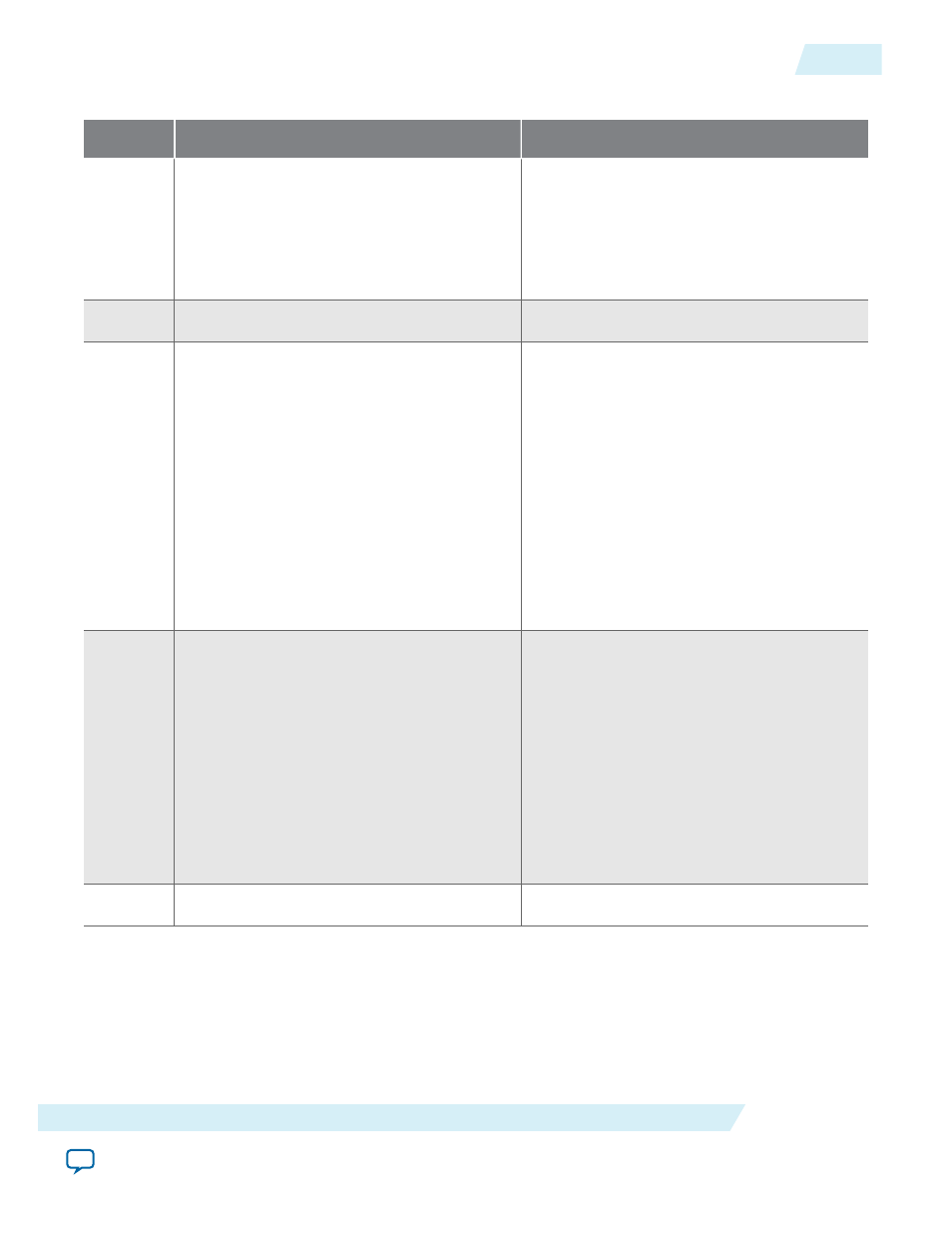

Table 4-11: Mapping Between tl_cfg_sts and Configuration Space Registers

tl_cfg_sts

Configuration Space Register

Description

[52:49] Device Status Register[3:0]

Records the following errors:

• Bit 3: unsupported request detected

• Bit 2: fatal error detected

• Bit 1: non-fatal error detected

• Bit 0: correctable error detected

[48]

Slot Status Register[8]

Data Link Layer state changed

[47]

Slot Status Register[4]

Command completed. (The hot plug

controller completed a command.)

Note: For Root Ports, you enable the

Slot register by turning on Use

Slot Power Register in the

parameter editor. When enabled,

access to Command Completed

Interrupt Enable bit of the Slot

Control register remains Read/

Write. This bit should be

hardwired to 1b'0. You should not

write this bit.

[46:31] Link Status Register[15:0]

Records the following link status informa‐

tion:

• Bit 15: link autonomous bandwidth status

• Bit 14: link bandwidth management status

• Bit 13: Data Link Layer link active

• Bit 12: Slot clock configuration

• Bit 11: Link Training

• Bit 10: Undefined

• Bits[9:4]: Negotiated Link Width

• Bits[3:0] Link Speed

[30]

Link Status 2 Register[0]

Current de-emphasis level.

UG-01105_avmm

2014.12.15

Hard IP Status Extension

4-19

Interfaces and Signal Descriptions

Altera Corporation