Altera Arria V Avalon-MM User Manual

Page 36

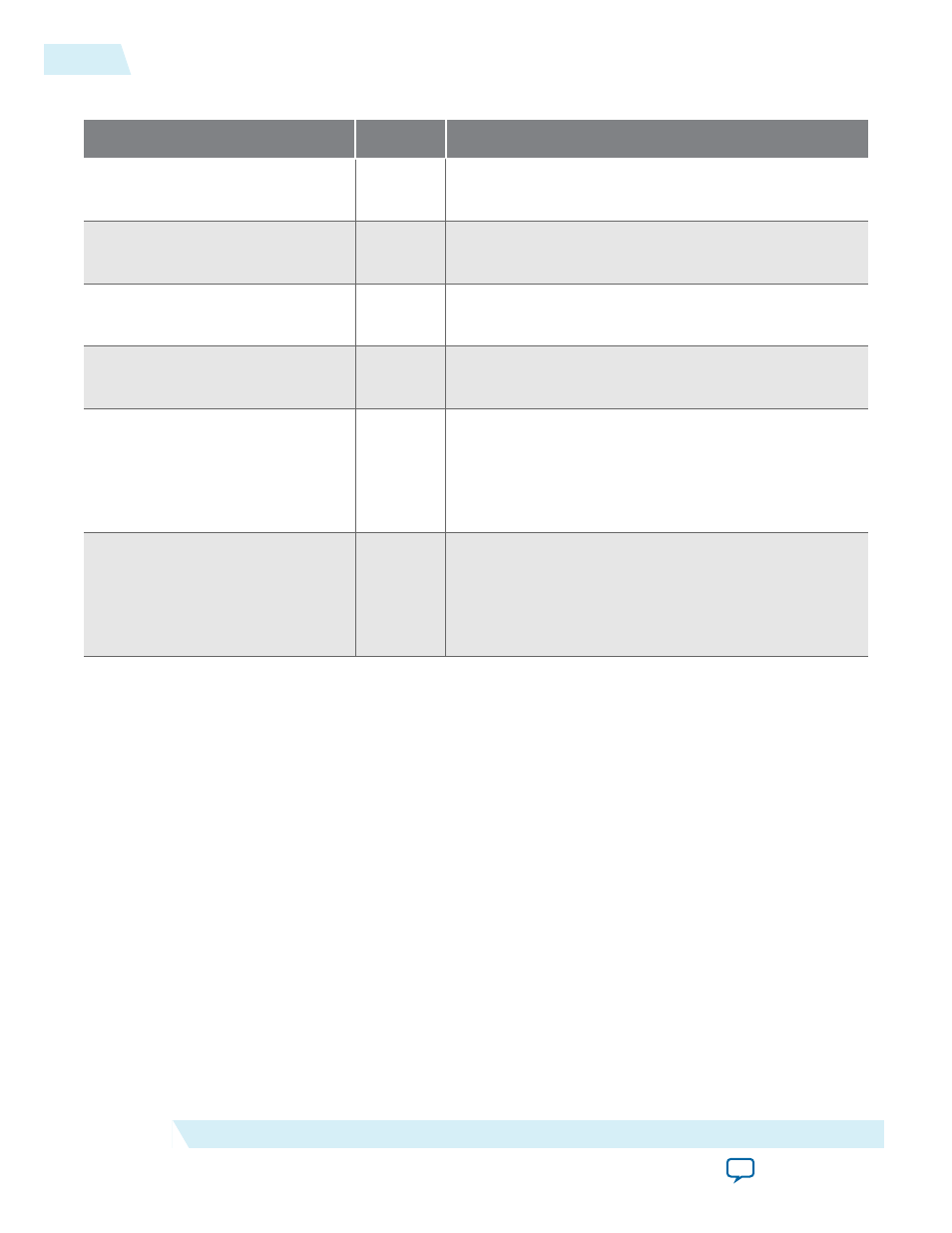

Table 4-3: Avalon-MM TX Slave Interface Signals

Signal Name

Direction

Description

TxsChipSelect_i

Input

The system interconnect fabric asserts this signal to

select the TX slave port.

TxsRead_i

Input

Read request asserted by the system interconnect fabric

to request a read.

TxsWrite_i

Input

Write request asserted by the system interconnect fabric

to request a write.

TxsWriteData[127 or 63:0]

Input

Write data sent by the external Avalon-MM master to

the TX slave port.

TxsBurstCount[6 or 5:0]

Input

Asserted by the system interconnect fabric indicating

the amount of data requested. The count unit is the

amount of data that is transferred in a single cycle, that

is, the width of the bus. The burst count is limited to 512

bytes.

TxsAddress_i[

Input

Address of the read or write request from the external

Avalon-MM master. This address translates to 64-bit or

32-bit PCI Express addresses based on the translation

table. The

created.

4-6

64- or 128-Bit Bursting TX Avalon-MM Slave Signals

UG-01105_avmm

2014.12.15

Altera Corporation

Interfaces and Signal Descriptions