Configurations – Altera Arria V Avalon-MM User Manual

Page 7

Configurations

The Avalon-MM Arria V Hard IP for PCI Express includes a full hard IP implementation of the PCI

Express stack comprising the following layers:

• Physical (PHY), including:

• Physical Media Attachment (PMA)

• Physical Coding Sublayer (PCS)

• Media Access Control (MAC)

• Data Link Layer (DL)

• Transaction Layer (TL)

When configured as an Endpoint, the Arria V Hard IP for PCI Express using the Avalon-MM supports

memory read and write requests and completions with or without data.

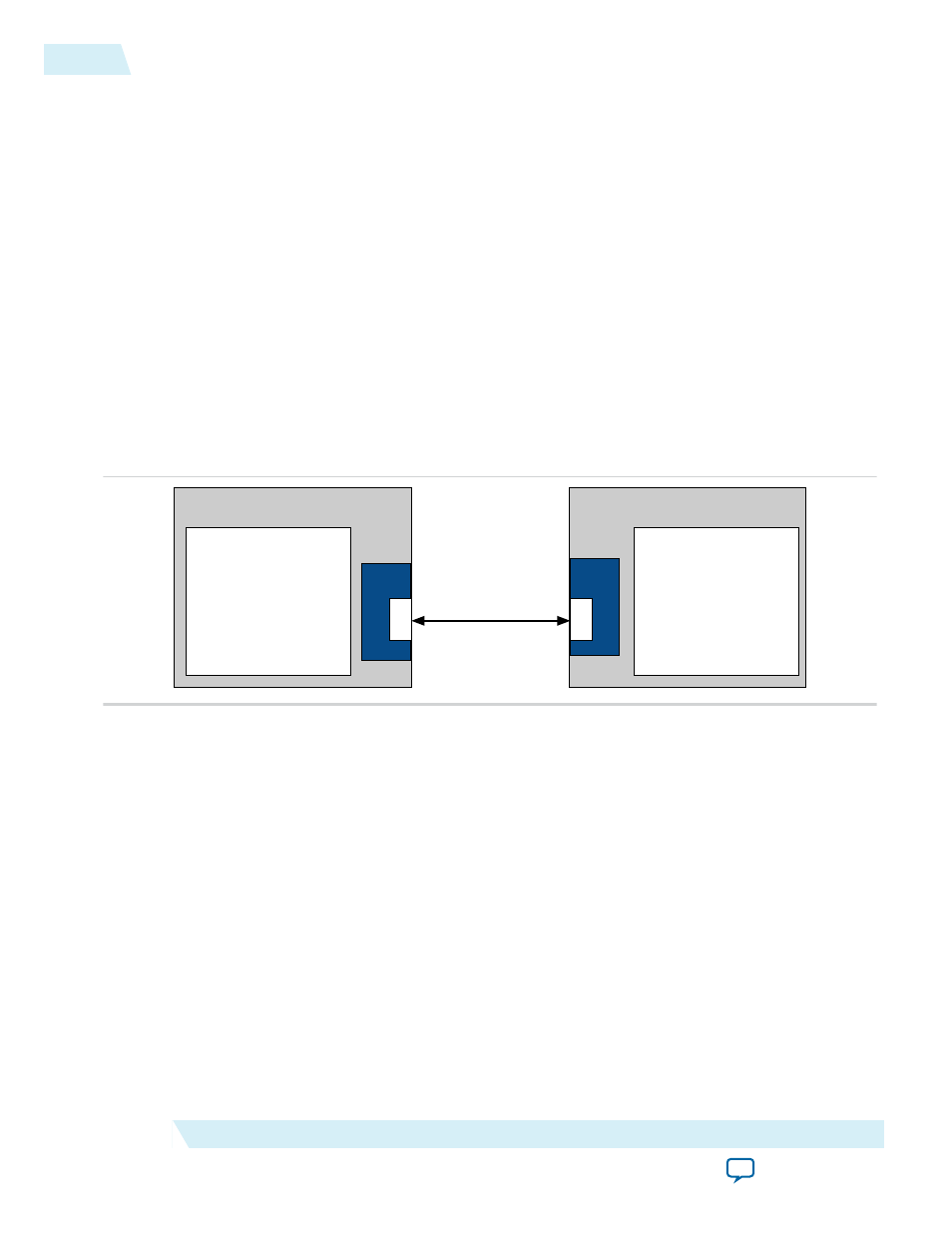

Figure 1-2: PCI Express Application with a Single Root Port and Endpoint

The following figure shows a PCI Express link between two Arria V FPGAs. One is configured as a Root

Port and the other as an Endpoint.

Altera FPGA

User Application

Logic

PCIe

Hard IP

RP

PCIe

Hard IP

EP

User Application

Logic

PCI Express Link

Altera FPGA

Figure 1-3: PCI Express Application Using Configuration via Protocol

The Arria V design below includes the following components:

• A Root Port that connects directly to a second FPGA that includes an Endpoint.

• Two Endpoints that connect to a PCIe switch.

• A host CPU that implements CvP using the PCI Express link connects through the switch. For more

information about configuration over a PCI Express link below.

1-6

Configurations

UG-01105_avmm

2014.12.15

Altera Corporation

Datasheet