Pci express mailbox registers – Altera Arria V Avalon-MM User Manual

Page 79

Bits

Name

Access

Description

[15:0]

AVL_IRQ_Vector

RO

Stores the interrupt vector of the system

interconnect fabric. The host software

should read this register after being

interrupted and determine the servicing

priority.

PCI Express Mailbox Registers

The PCI Express Root Complex typically requires write access to a set of PCI Express-to-Avalon-MM

mailbox registers and read-only access to a set of Avalon-MM-to-PCI Express mailbox registers. Eight

mailbox registers are available.

The

PCI Express-to-Avalon-MM Mailbox

registers are writable at the addresses shown in the following

table. Writing to one of these registers causes the corresponding bit in the

Avalon-MM Interrupt

Status

register to be set to a one.

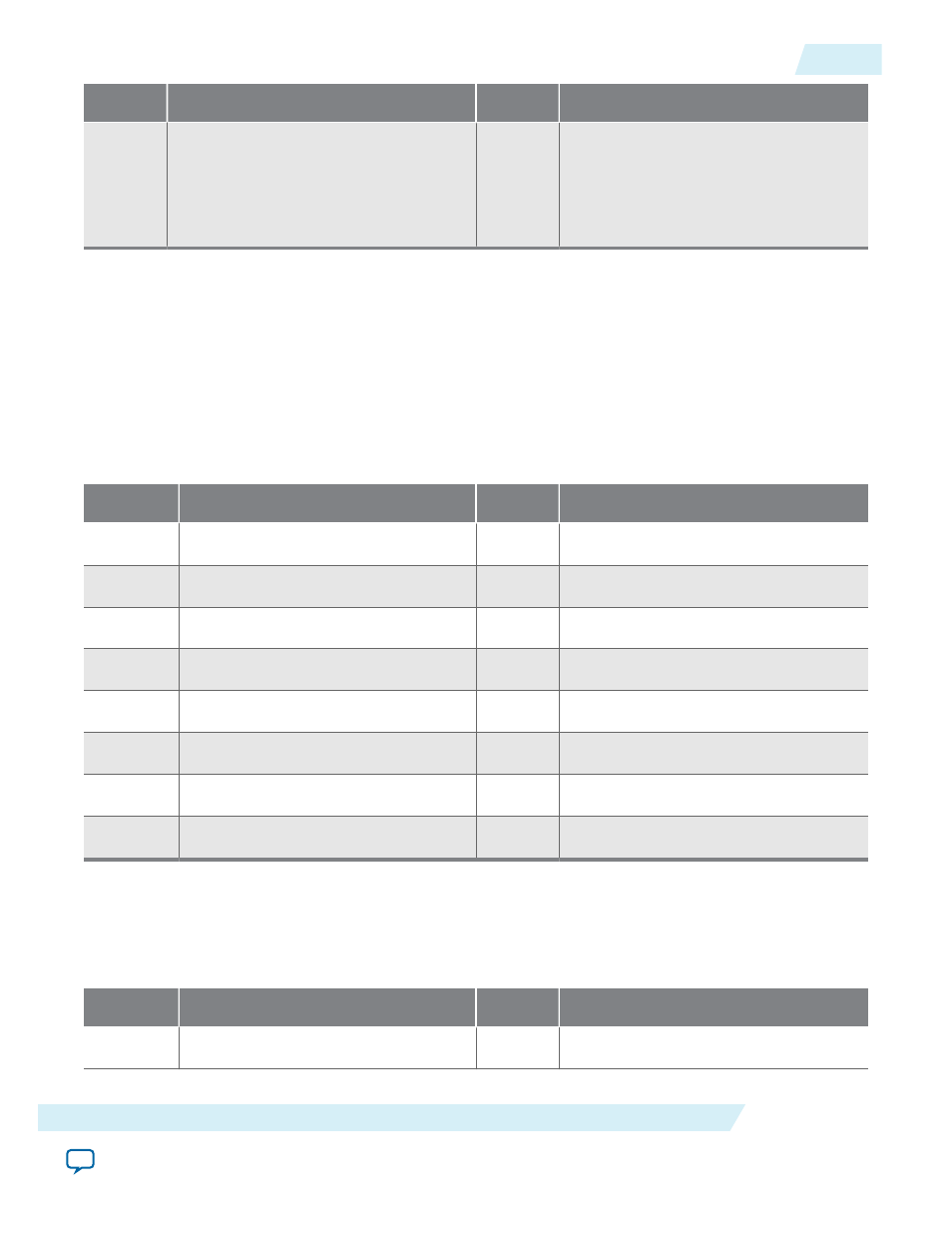

Table 5-16: PCI Express-to-Avalon-MM Mailbox Registers, 0x0800–0x081F

Address

Name

Access

Description

0x0800

P2A_MAILBOX0

RW

PCI Express-to-Avalon-MM Mailbox 0

0x0804

P2A_MAILBOX1

RW

PCI Express-to-Avalon-MM Mailbox 1

0x0808

P2A_MAILBOX2

RW

PCI Express-to-Avalon-MM Mailbox 2

0x080C

P2A_MAILBOX3

RW

PCI Express-to-Avalon-MM Mailbox 3

0x0810

P2A_MAILBOX4

RW

PCI Express-to-Avalon-MM Mailbox 4

0x0814

P2A_MAILBOX5

RW

PCI Express-to-Avalon-MM Mailbox 5

0x0818

P2A_MAILBOX6

RW

PCI Express-to-Avalon-MM Mailbox 6

0x081C

P2A_MAILBOX7

RW

PCI Express-to-Avalon-MM Mailbox 7

The

Avalon-MM-to-PCI Express Mailbox

registers are read at the addresses shown in the following

table. The PCI Express Root Complex should use these addresses to read the mailbox information after

being signaled by the corresponding bits in the

Avalon

MM to PCI Express Interrupt Status

register.

Table 5-17: Avalon-MM-to-PCI Express Mailbox Registers, 0x0900–0x091F

Address

Name

Access

Description

0x0900

A2P_MAILBOX0

RO

Avalon-MM-to-PCI Express Mailbox 0

UG-01105_avmm

2014.12.15

PCI Express Mailbox Registers

5-17

Registers

Altera Corporation