Completer only single dword endpoint – Altera Arria V Avalon-MM User Manual

Page 135

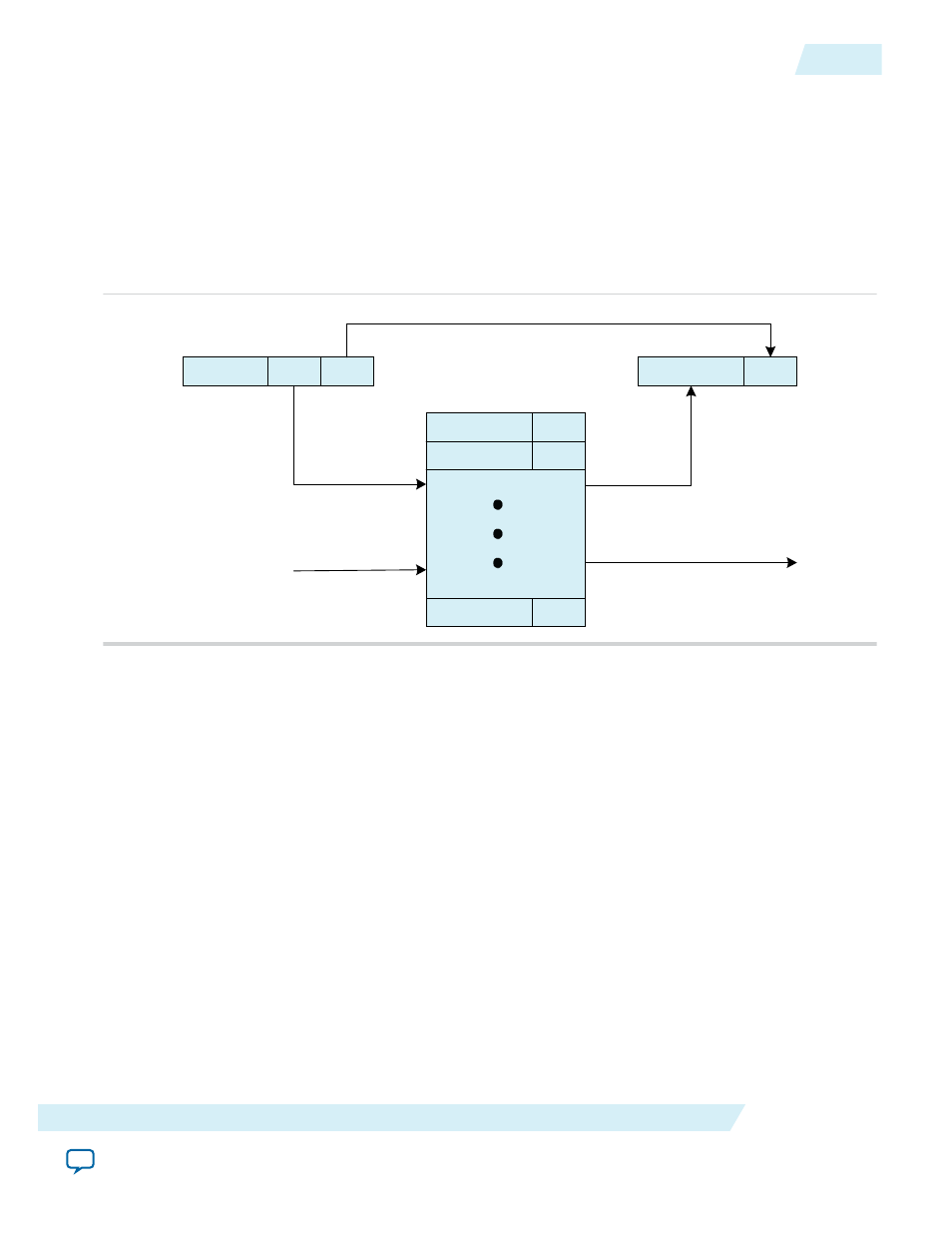

Figure 9-10: Avalon-MM-to-PCI Express Address Translation

The following figure depicts the Avalon-MM-to-PCI Express address translation process. In this figure

the variables represent the following paramers:

• N—the number of pass-through bits.

• M—the number of Avalon-MM address bits.

• P—the number of PCIe address bits.

• Q—the number of translation table entries.

•

Sp[1:0]

—the space indication for each entry.

PCIe Address Q-1

SpQ-1

Space Indication

PCI Express address from Table Entry

becomes High PCI Express address bits

PCI Express Address

High

Low

P-1

N N-1

0

Low address bits unchanged

Avalon-MM-to-PCI Express

Address Translation Table

(Q entries by P-N bits wide)

PCIe Address 0

Sp0

PCIe Address 1

Sp1

Avalon-MM Address

High

Slave Base

Address

Low

M-1

31

M

N N-1

0

Table updates from

control register port

High Avalon-MM Address

Bits Index table

Completer Only Single Dword Endpoint

The completer only single dword endpoint is intended for applications that use the PCI Express protocol

to perform simple read and write register accesses from a host CPU. The completer only single dword

endpoint is a hard IP implementation available for Qsys systems, and includes an Avalon-MM interface to

the Application Layer. The Avalon-MM interface connection in this variation is 32 bits wide. This

endpoint is not pipelined; at any time a single request can be outstanding.

The completer-only single dword endpoint supports the following requests:

• Read and write requests of a single dword (32 bits) from the Root Complex

• Completion with Completer Abort status generation for other types of non-posted requests

• INTX or MSI support with one Avalon-MM interrupt source

UG-01105_avmm

2014.12.15

Completer Only Single Dword Endpoint

9-19

IP Core Architecture

Altera Corporation