Test, Figure d-1, Appendix d – Digilent 6003-410-000P-KIT User Manual

Page 97

XUP Virtex-II Pro Development System

97

UG069 (v1.0) March 8, 2005

1-800-255-7778

R

Appendix D

Using the Golden FPGA Configuration

for System Self-Test

A special design has been placed in the Platform FLASH PROM to provide a Built-in Self-

Test (BIST) boot/configuration that tests critical board features and reports on board health

and status.

Appendix C, “Restoring the Golden FPGA Configuration,”

of this document covers the

details of restoring the BIST design if it has been erased accidentally. This feature puts the

board through several tests to verify the board is fully functional in a stand-alone

environment. Other tests to verify system-level functionality can be supported via

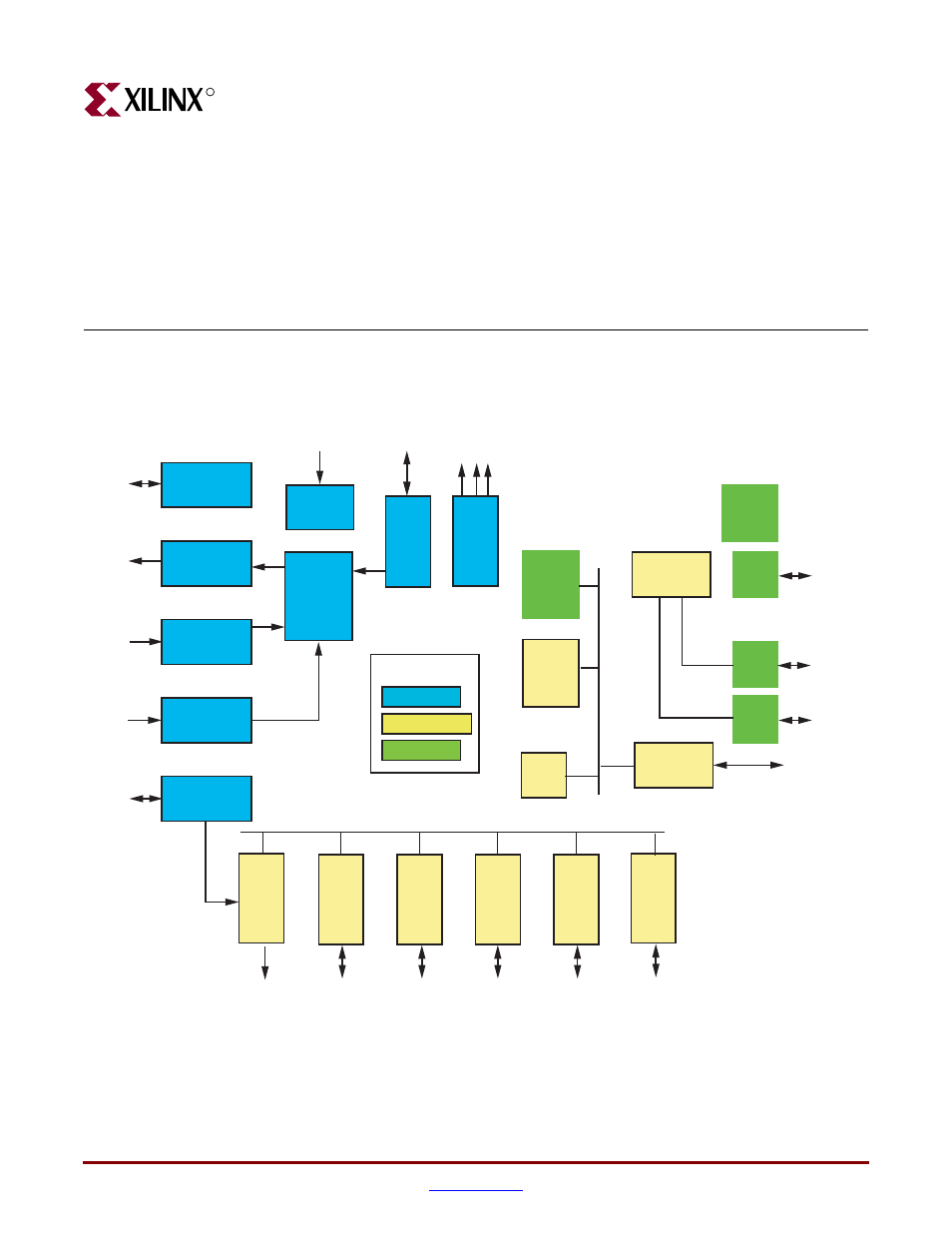

Figure D-1:

XUP Virtex-II Pro Development System BIST Block Diagram

Audio Tones &

Push Buttons

VGA

Keyboard

PS2

LEDs &

DIP Switches

Clock

Generator

Char. &

Test

Pattern

Generator

Silicon

Ser Number

Exter

nal

Po

rt

T

e

s

t

PPC 0

PPC 1

PLB AT

BRAM

128 Kb

PLB

BUS

OPB BUS

MGT

MGT

MGT

DDR SDRAM

CONTROL

Bridge

Key

HARDWARE

PROC PERIPH

HARD IP

UG069_20_010605

UA

R

T

LITE

GPIO

II C

CNTRL

A

C

97

CNTRL

ETHERNET

MA

C

SYSA

CE

CONTRL

UA

R

T

LITE