Digilent 6003-410-000P-KIT User Manual

Page 33

XUP Virtex-II Pro Development System

33

UG069 (v1.0) March 8, 2005

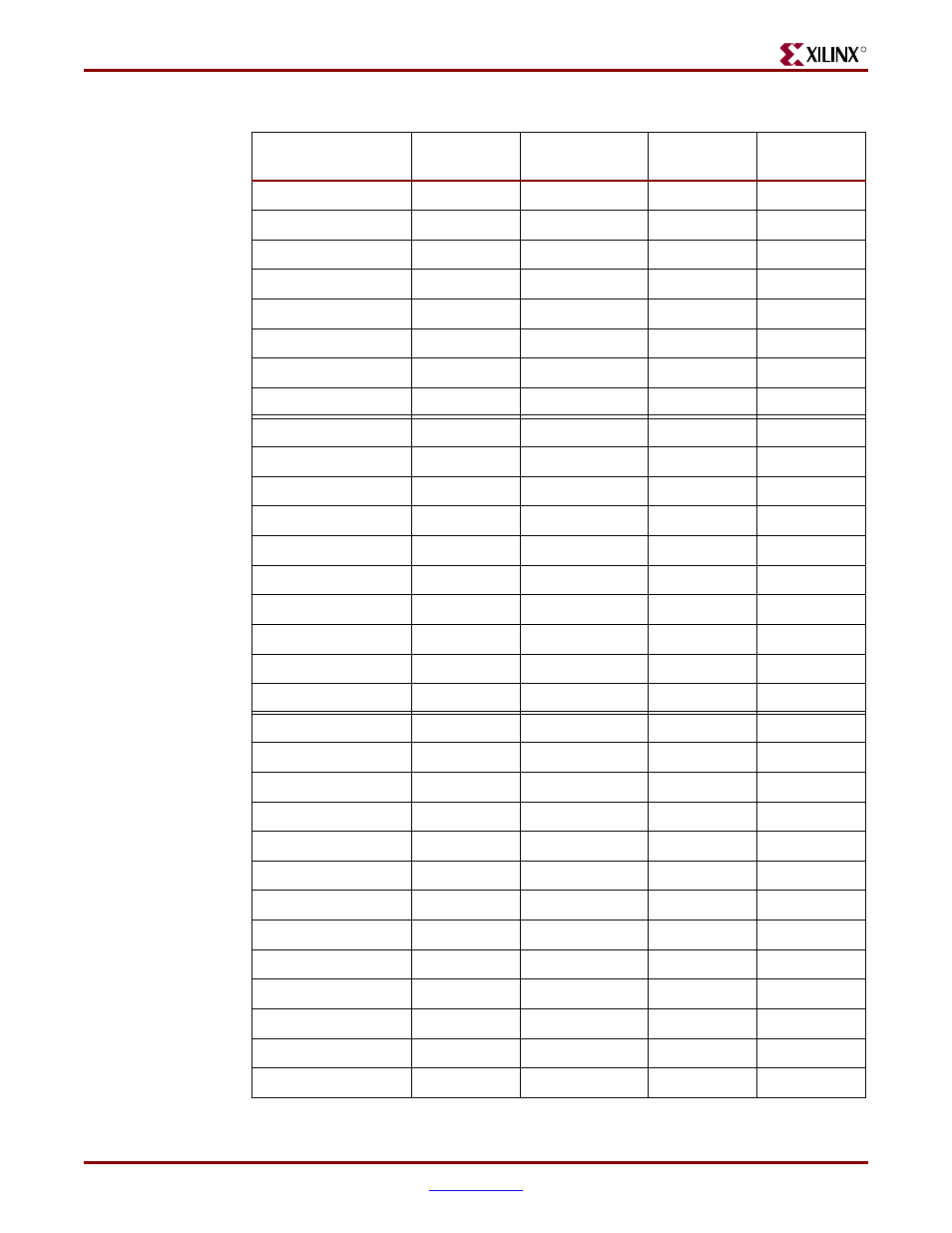

Using the DIMM Module DDR SDRAM

R

SDRAM_DQ[58]

I/O

87

AG29

SSTL2-II

SDRAM_DQ[59]

I/O

88

AD26

SSTL2-II

SDRAM_DQ[60]

I/O

174

AD25

SSTL2-II

SDRAM_DQ[61]

I/O

175

AG28

SSTL2-II

SDRAM_DQ[62]

I/O

178

AH27

SSTL2-II

SDRAM_DQ[63]

I/O

179

AH29

SSTL2-II

SDRAM_DQS[7]

I/O

86

AH26

SSTL2-II

SDRAM_DM[7]

0

177

W25

SSTL2-II

SDRAM_CB[0]

I/O

44

R28

SSTL2-II

SDRAM_CB[1]

I/O

45

U30

SSTL2-II

SDRAM_CB[2]

I/O

49

V30

SSTL2-II

SDRAM_CB[3]

I/O

51

T26

SSTL2-II

SDRAM_CB[4]

I/O

134

T25

SSTL2-II

SDRAM_CB[5]

I/O

135

T28

SSTL2-II

SDRAM_CB[6]

I/O

142

T27

SSTL2-II

SDRAM_CB[7]

I/O

144

U28

SSTL2-II

SDRAM_DQS[8]

I/O

47

T23

SSTL2-II

SDRAM_DM[8]

0

140

U22

SSTL2-II

SDRAM_A[0]

O

48

M25

SSTL2-II

SDRAM_A[1]

O

43

N25

SSTL2-II

SDRAM_A[2]

O

41

L26

SSTL2-II

SDRAM_A[3]

O

130

M29

SSTL2-II

SDRAM_A[4]

O

37

K30

SSTL2-II

SDRAM_A[5]

O

32

G25

SSTL2-II

SDRAM_A[6]

O

125

G26

SSTL2-II

SDRAM_A[7]

O

29

D26

SSTL2-II

SDRAM_A[8]

O

122

J24

SSTL2-II

SDRAM_A[9]

O

27

K24

SSTL2-II

SDRAM_A[10]

O

141

F28

SSTL2-II

SDRAM_A[11]

O

118

F30

SSTL2-II

SDRAM_A[12]

O

115

M24

SSTL2-II

Table 2-5:

DDR SDRAM Connections (Continued)

Signal

Direction

DIMM

Module Pin

FPGA

Pin

I/O Type