Figure 2-20, Table 2-21 – Digilent 6003-410-000P-KIT User Manual

Page 68

68

XUP Virtex-II Pro Development System

UG069 (v1.0) March 8, 2005

Chapter 2: Using the System

R

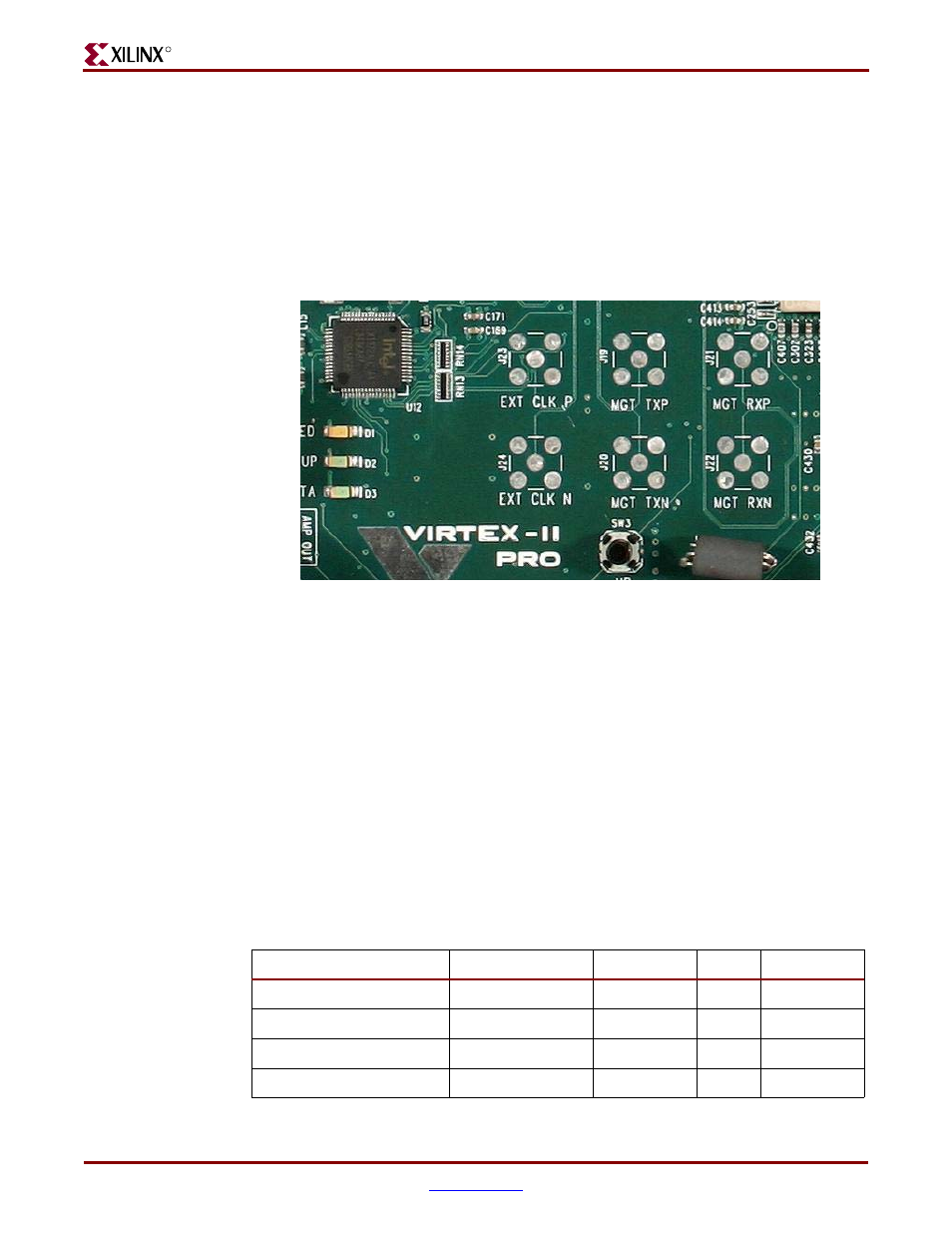

The fourth MGT channel pair terminates on user_supplied SMA connectors (J19-22) and

can be driven by a user_supplied differential clock input pair, EXTERNAL_CLOCK_P and

EXTERNAL_CLOCK_N provided on SMA connectors (J23-24). This EXTERNAL_CLOCK

can be used to clock the SATA ports if non-standard signaling rates are required. The MGT

connections are shown in

For the user to take advantage of the fourth MGT channel, four SMA connectors must be

installed at J19-J22. These SMA connectors can be purchased from Digikey under the part

number A24691-ND.

identifies the location of the external differential clock

inputs.

There are eight clock inputs into each RocketIO™ transceiver instantiation. REFCLK and

BREFCLK are reference clocks generated from an external source and presented to the

FPGA as differential inputs. The reference clocks connect to the REFCLK or BREFCLK

ports on the RocketIO MGT. While only one of these reference clocks is needed to drive the

MGT, BREFCLK or BREFCLK2 must be used for serial speeds of 2.5 Gb/s or greater.

At speeds of 2.5 Gb/s or greater, REFCLK configuration introduces more than the

maximum allowable jitter to the RocketIO transceiver. For these higher speeds, BREFCLK

configuration is required. The BREFCLK configuration uses dedicated routing resources

that reduce jitter. BREFCLK enters the FPGA through a dedicated clock input buffer.

BREFCLK can connect to the BREFCLK inputs of the MGT and the CLKIN input of a DCM

for creation of user clocks.

The SATA data rate is less than 2.5 Gb/s so the 75 MHz clocks could have been supplied in

the REFCLK inputs, but for consistency the BREFCLK and BREFCLK2 clock inputs are

used for the on-board and user-supplied MGT clocks as shown in

.

Figure 2-20:

SMA-based MGT Connections

Table 2-21:

SATA and MGT Signals

Signal

MGT Location

PAD Name

I/O Pin

Notes

SATA_PORT0_TXN

MGT_X0Y1

TXNPAD4

A27

HOST

SATA_PORT0_TXP

MGT_X0Y1

TXPPAD4

A26

–

SATA_PORT0_RXN

MGT_X0Y1

RXNPAD4

A24

–

SATA_PORT0_RXP

MGT_X0Y1

RXPPAD4

A25

–