Digilent 6003-410-000P-KIT User Manual

Page 69

XUP Virtex-II Pro Development System

69

UG069 (v1.0) March 8, 2005

Using the Multi-Gigabit Transceivers

R

The RocketIO MGTs utilize differential signaling between the transmit and receive data

ports to minimize the effects of common mode noise and signal crosstalk. With the use of

high-speed serial transceivers, the interconnect media causes degradation of the signal at

the receiver. Effects such as inter-symbol interference (ISI) or data dependent jitter are

produced. This loss can be large enough to degrade the eye pattern opening at the receiver

beyond that which results in reliable data transmission. The RocketIO MGTs allow the user

to set the initial differential voltage swing and signal pre-emphasis to negate a portion of

the signal degradation to increase the reliability of the data transmission.

In pre-emphasis, the initial differential voltage swing is boosted to create a stronger rising

or falling waveform. This method compensates for high frequency loss in the transmission

media that would otherwise limit the magnitude of the received waveform.

The initial differential voltage swing and signal pre-emphasis are set by two user-defined

RocketIO transceiver attributes. The TX_DIFF_CTRL attribute sets the voltage difference

between the differential lines, and the TX_PREEMPHASIS attribute sets the output driver

pre-emphasis.

Xilinx recommends setting the TX_DIF_CTRL attribute to 600 (600 mV) and the

TXPREEMPHASIS attribute to 2 (25%) when SATA cables of 1.0 or less meters in length are

used to connect the MGT host to the MGT target. Typical eye diagrams for 1.5 Gb/s data

SATA_PORT0_IDLE

–

–

B15

–

SATA_PORT1_TXN

MGT_X1Y1

TXNPAD6

A20

TARGET

SATA_PORT1_TXP

MGT_X1Y1

TXPPAD6

A19

–

SATA_PORT1_RXN

MGT_X1Y1

RXNPAD6

A17

–

SATA_PORT1_RXP

MGT_X1Y1

RXPPAD6

A18

–

SATA_PORT1_IDLE

–

–

AK3

–

SATA_PORT2_TXN

MGT_X2Y1

TXNPAD7

A14

HOST

SATA_PORT2_TXP

MGT_X2Y1

TXPPAD7

A13

–

SATA_PORT2_RXN

MGT_X2Y1

RXNPAD7

A11

–

SATA_PORT2_RXP

MGT_X2Y1

RXPPAD7

A12

–

SATA_PORT2_IDLE

–

–

C15

–

MGT_TXN

MGT_X3Y1

TXNPAD9

A7

USER

MGT_TXP

MGT_X3Y1

TXPPAD9

A6

–

MGT_RXN

MGT_X3Y1

RXNPAD9

A4

–

MGT_RXP

MGT_X3Y1

RXPPAD9

A5

–

MGT_CLK_N

–

–

G16

BREFCLK

MGT_CLK_P

–

–

F16

–

EXTERNAL_CLOCK_N

–

–

F15

BREFCLK2

EXTERNAL_CLOCK_P

–

–

G15

–

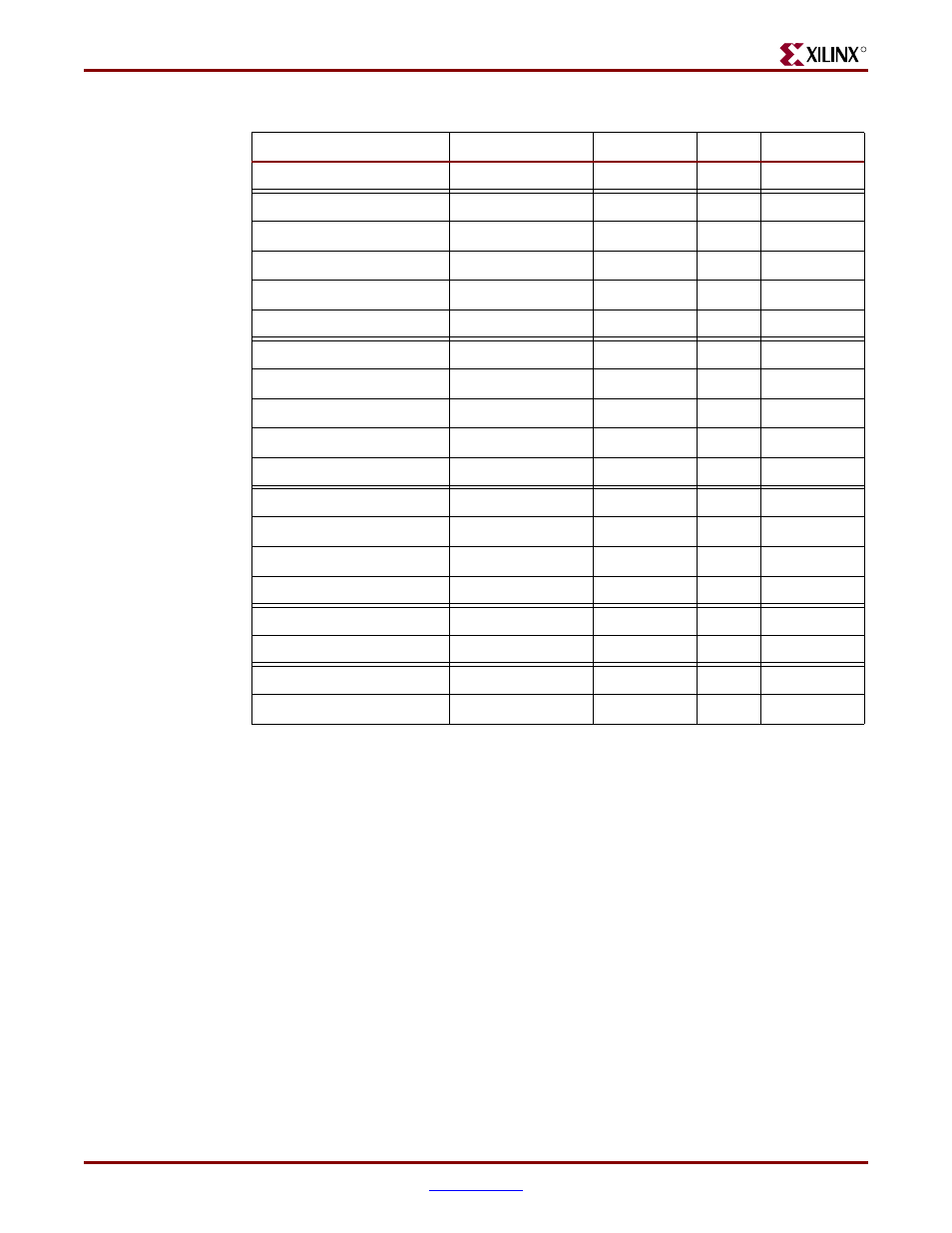

Table 2-21:

SATA and MGT Signals (Continued)

Signal

MGT Location

PAD Name

I/O Pin

Notes