Figure 2-19, Table 2-19 – Digilent 6003-410-000P-KIT User Manual

Page 64

64

XUP Virtex-II Pro Development System

UG069 (v1.0) March 8, 2005

Chapter 2: Using the System

R

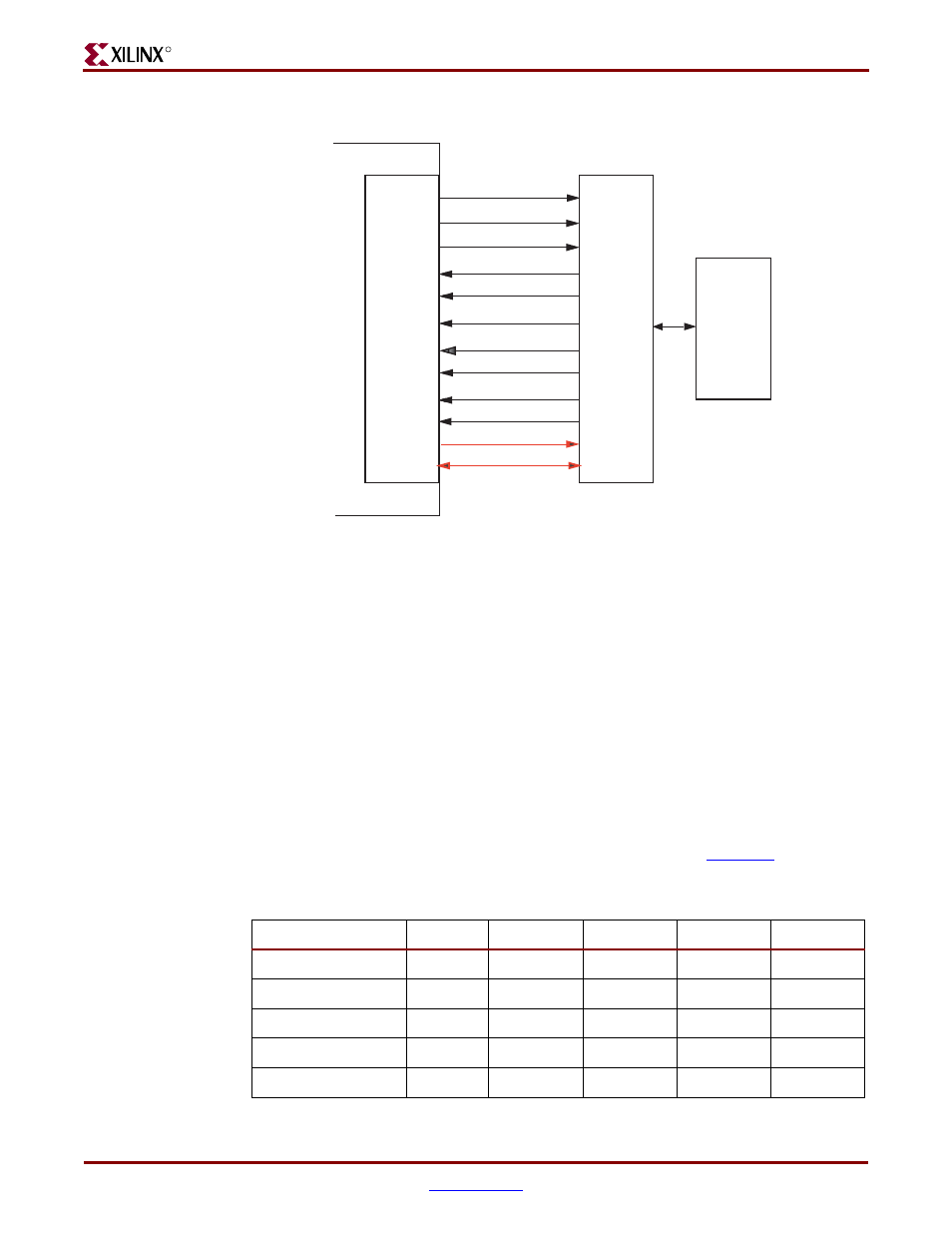

provides a block diagram of the Ethernet interface.

The XUP Virtex-II Pro Development System includes a Dallas Semiconductor DS2401P

Silicon Serial Number (U13). This device provides a unique identity for each circuit board

which can be determined with a minimal electronic interface. The DS2401P consists of a

factory laser programmed, 64-bit ROM that includes a unique 48-bit serial number, an 8-bit

CRC, and an 8-bit family device code. Data is transferred serially via the 1-Wire protocol,

which requires only a single data lead and a ground return. Power for reading the device

is derived from the data line with no requirement for an additional power supply. The

unique 48-bit serial number should not be used as the MAC address for the Ethernet

interface, because this number has not been registered as a valid Ethernet MAC address.

The XUP Virtex-II Pro Development System printed circuit board includes a label that

contains the board serial number, obtained from the DS2401P Silicon Serial Number, as

well as a valid Ethernet MAC address that has been registered with the IEEE. Xilinx

maintains a cross reference list matching the board serial number with the assigned

Ethernet MAC address on the XUP Virtex-II Pro Development System support Web page.

Xilinx provides the IP for the 1-Wire interface and application

Synthesizable

FPGA Interface for Retrieving ROM Number from 1-Wire Devices describes this interface.

Figure 2-19:

10/100 Ethernet Interface Block Diagram

Table 2-19:

10/100 ETHERNET Connections

Signal

Direction

FPGA Pin

I/O Type

Drive

Slew

TX_DATA[0]

O

J7

LVTTL

8 mA

SLOW

TX_DATA[1]

O

J8

LVTTL

8 mA

SLOW

TX_DATA[2]

O

C1

LVTTL

8 mA

SLOW

TX_DATA[3]

O

C2

LVTTL

8 mA

SLOW

TX_ERROR

O

H2

LVTTL

8 mA

SLOW

LXT972A

RJ-45

FPGA

MAC IP

TX_ERROR

TX_ENABLE

TX_DATA[3:0]

RX_CLOCK

RX_DATA[3:0]

RX_ERROR

RX_DATA_VALID

CARRIER_SENSE

COLLISION

MDC

MDIO

TX_CLOCK

UG069_19_012505

Magnetics