Expansion port test, Additional hardware required, Test procedure – Digilent 6003-410-000P-KIT User Manual

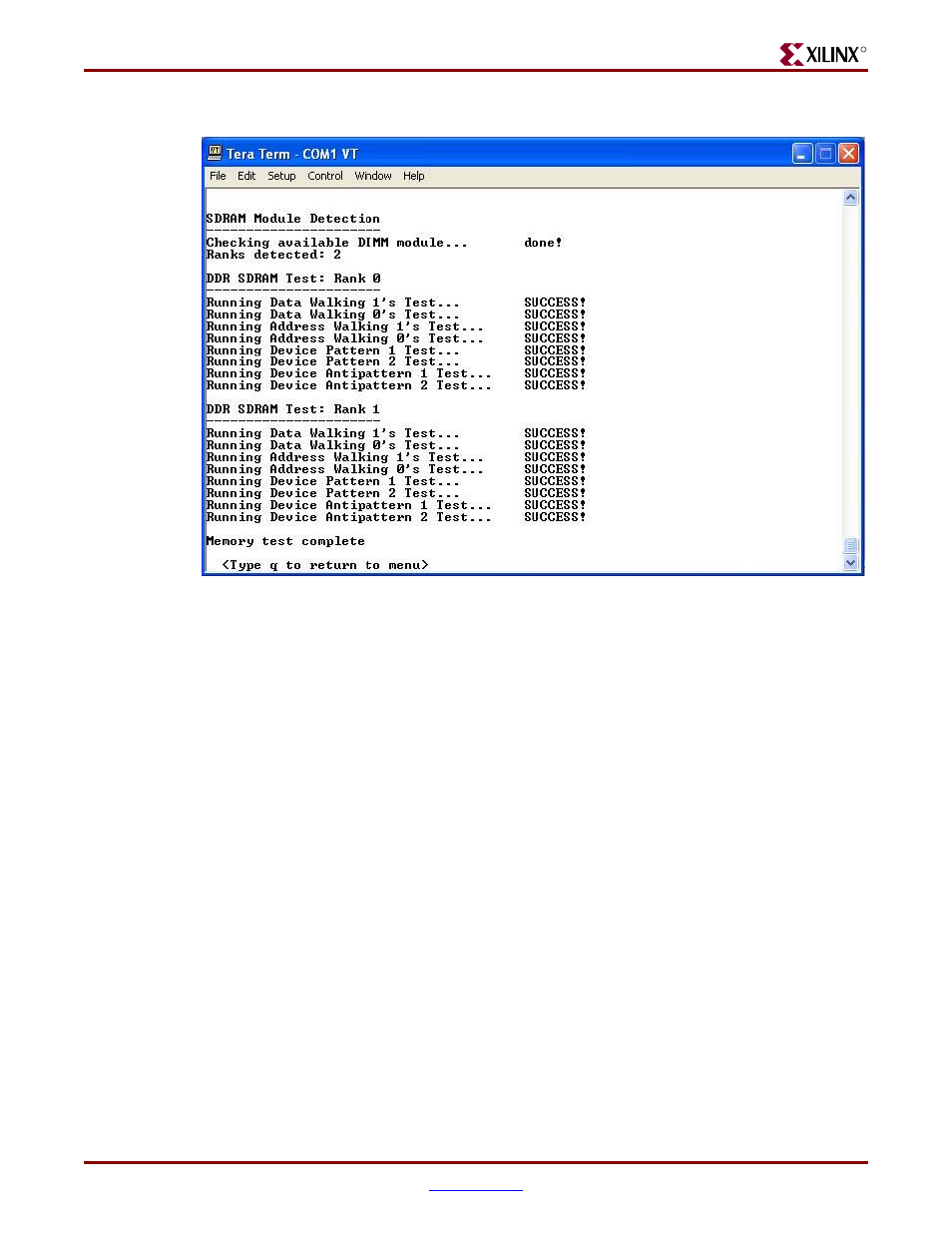

Page 113: Figure d-20

XUP Virtex-II Pro Development System

113

UG069 (v1.0) March 8, 2005

1-800-255-7778

Processor-Based Tests

R

2.

In the case of an error, the following is an example of what would be printed:

Running Data Walking 1’s Test…FAILED!

Address: 0x00000000, Expected: 0x0000000000000001, Actual:

0x0000000100000001

Expansion Port Test

This test verifies the connectivity of the FPGA to the four expansion headers, the two low-

speed expansion ports, and the single high-speed expansion port. The design creates a

walking one pulse across the 80-bit expansion bus. This test signal is also applied to the 64-

bit low-speed Digilent expansion port and the 43-bit high-speed Digilent expansion port.

It is important that no expansion boards be connected to the XUP Virtex-II Pro

Development System when this test is running. This is to avoid any potential contention

between the outputs of the FPGA driving the expansion ports and any output from the

installed expansion boards.

Additional Hardware Required

•

Oscilloscope

Test Procedure

1.

This test begins when “6” is selected from the BIST Main menu. It checks the

functionality of the low-speed and high-speed expansion ports.

2.

There is a second prompt before the test starts, as shown in

.

Figure D-20:

DDR SDRAM Test Completion