Figure d-21 – Digilent 6003-410-000P-KIT User Manual

Page 114

114

XUP Virtex-II Pro Development System

1-800-255-7778

UG069 (v1.0) March 8, 2005

Appendix D: Using the Golden FPGA Configuration for System Self-Test

R

3.

Connect the oscilloscope ground lead to any of the pins on the top row of J1-J4. These

are all ground (GND) pins. If J1-J4 are not installed, then connect the oscilloscope

ground lead to the GND pin of J36, the “DEBUG PORT.” This pin is clearly identified

on the PCB silkscreen.

4.

Sequentially, check each of the non-power pins on the lower rows of J1-J4. You should

see a 20 ns pulse with a 1.6

µs period at each pin. If the pulse is not observed, there is a

broken trace on the PCB, or the level shifters are damaged. If the period is not correct,

two non-adjacent signals are shorted together. If the pulse width is not correct, two or

more adjacent signals are shorted together.

Note:

The low-speed Digilent expansion ports (J5-J6) are wired in parallel with the header pins

J1-J4.

5.

Sequentially, check each of the non-power pins on the signal row of the high-speed

Digilent expansion connector J37. The signal row of this connector is the row farthest

from the mating edge of the connector. You should see a 20 ns pulse with a 1.6

µs

period at each signal pin.

Note:

The five pins on each end of the signal row are either power pins or JTAG pins and will

not have the test pattern applied to them.

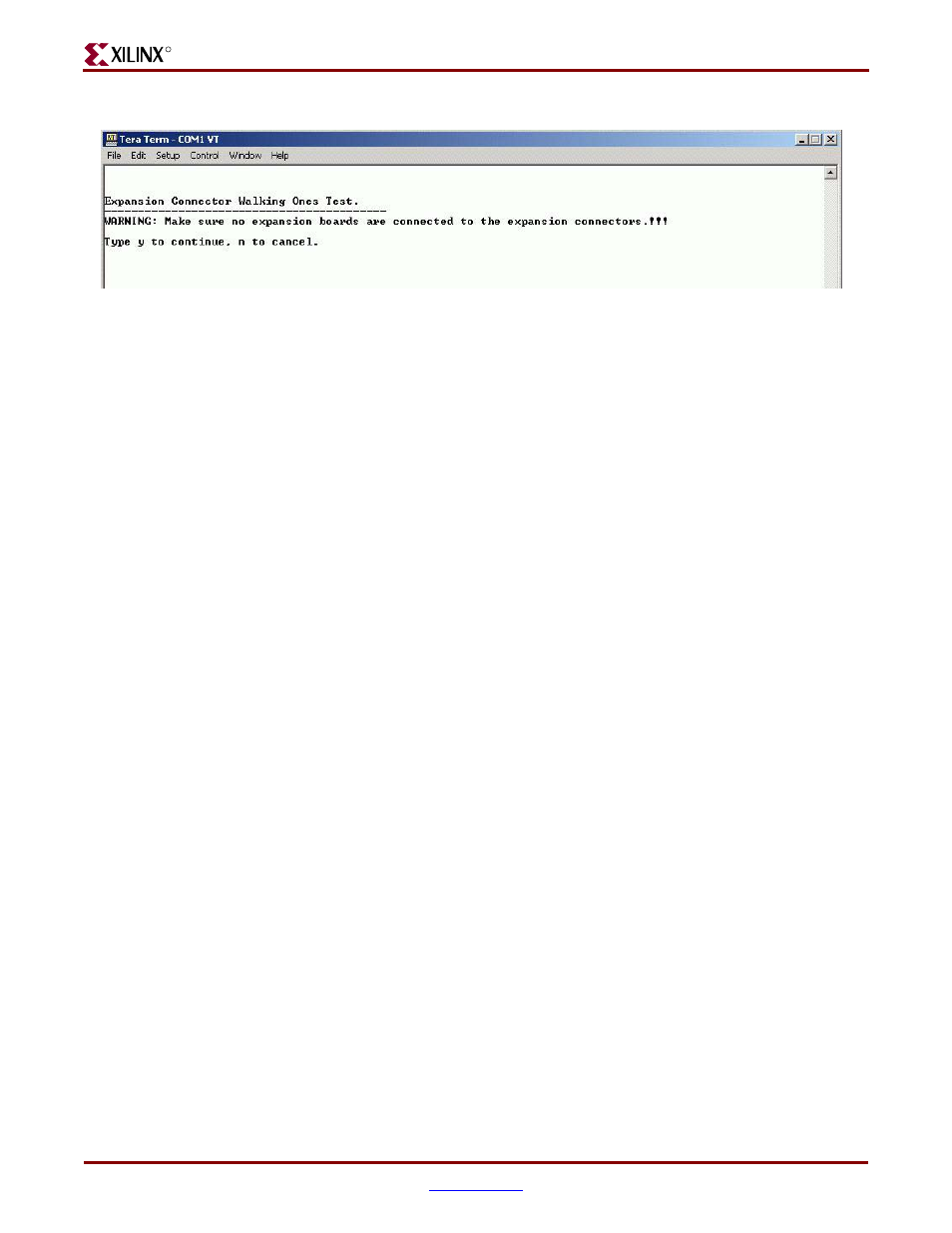

Figure D-21:

Confirming Start of the Expansion Port Walking Ones Test

ug076_21_021005