Digilent 6003-410-000P-KIT User Manual

Page 48

48

XUP Virtex-II Pro Development System

UG069 (v1.0) March 8, 2005

Chapter 2: Using the System

R

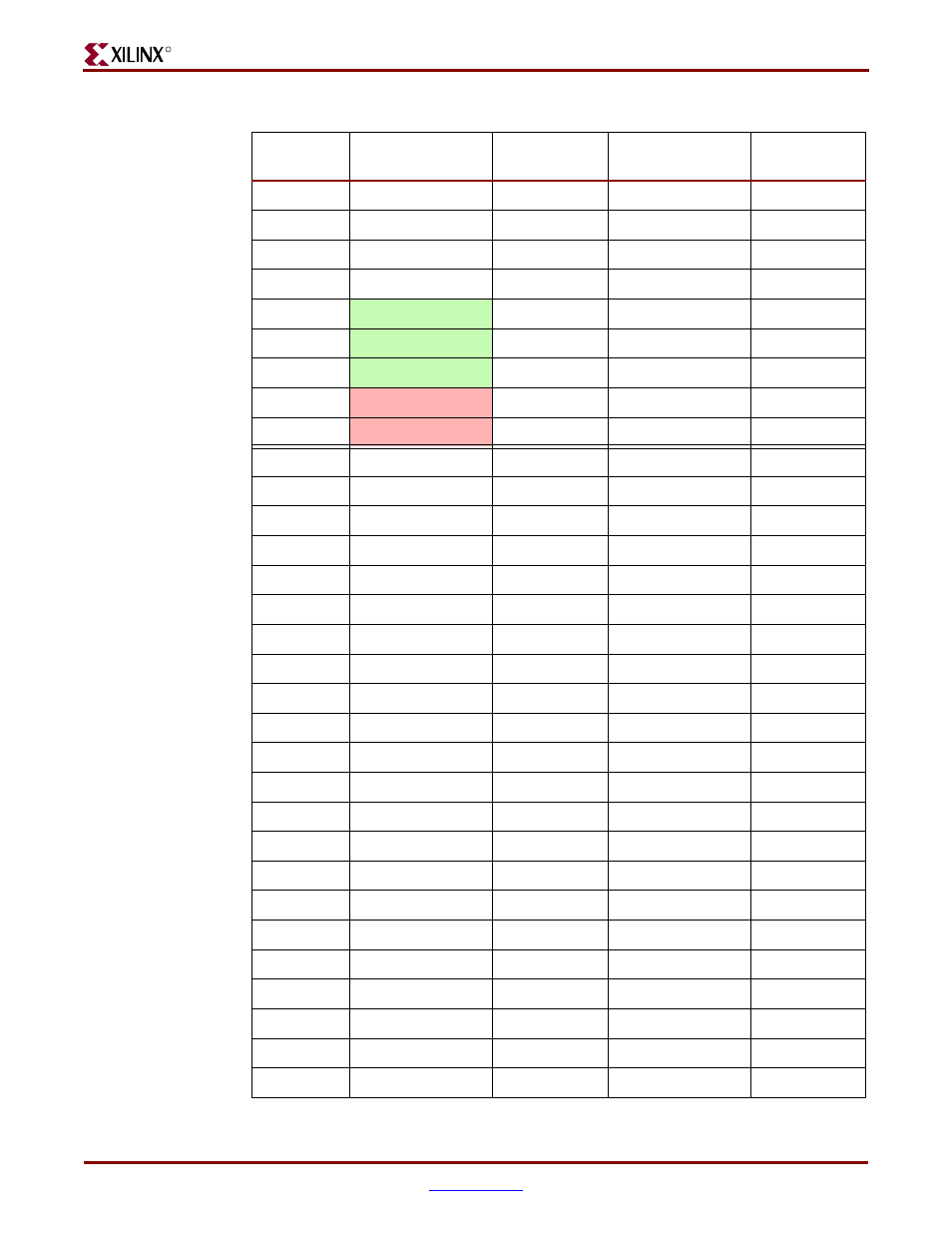

43

EXP_IO_36

U1

J5.32

LVTTL

45

EXP_IO_37

V1

J5.33

LVTTL

47

EXP_IO_38

T5

J5.34

LVTTL

49

EXP_IO_39

T6

J5.35

LVTTL

51

VCC3V3

–

J5.3 J6.3

–

53

VCC3V3

–

J5.3 J6.3

–

55

VCC3V3

–

J5.3 J6.3

–

57

VCC5V0

–

J5.2 J6.2

–

59

VCC5V0

–

J5.2 J6.2

–

2

GND

–

J5.1 J6.1

–

4

GND

–

J5.1 J6.1

–

6

GND

–

J5.1 J6.1

–

8

GND

–

J5.1 J6.1

–

10

GND

–

J5.1 J6.1

–

12

GND

–

J5.1 J6.1

–

14

GND

–

J5.1 J6.1

–

16

GND

–

J5.1 J6.1

–

18

GND

–

J5.1 J6.1

–

20

GND

–

J5.1 J6.1

–

22

GND

–

J5.1 J6.1

–

24

GND

–

J5.1 J6.1

–

26

GND

–

J5.1 J6.1

–

28

GND

–

J5.1 J6.1

–

30

GND

–

J5.1 J6.1

–

32

GND

–

J5.1 J6.1

–

34

GND

–

J5.1 J6.1

–

36

GND

–

J5.1 J6.1

–

38

GND

–

J5.1 J6.1

–

40

GND

–

J5.1 J6.1

–

42

GND

–

J5.1 J6.1

–

44

GND

–

J5.1 J6.1

–

Table 2-11:

Upper Middle Expansion Header Pinout (Continued)

J2|

Pin

Signal

FPGA

Pin

Digilent

EXP Pin

IO Type

See also other documents in the category Digilent Hardware:

- 410-282P-KIT (4 pages)

- 410-279P-KIT (26 pages)

- 410-258P-KIT (16 pages)

- 410-138P-KIT (28 pages)

- 410-178P-KIT (22 pages)

- 410-292P-KIT (29 pages)

- 410-274P-KIT (29 pages)

- 410-182P-KIT (22 pages)

- 410-134P-KIT (17 pages)

- 410-183P-KIT (19 pages)

- 410-155P-KIT (12 pages)

- 6015-410-001P-KIT (26 pages)

- 410-087P-KIT (164 pages)

- 410-146P-KIT (4 pages)

- XUPV2P (23 pages)

- 410-047-C2P-KIT (3 pages)

- WaveForms (85 pages)

- 410-297P-KIT (25 pages)

- 410-295P-KIT (37 pages)

- 410-296P-KIT (23 pages)

- 410-209P-KIT REV.D (16 pages)

- 410-209P-KIT REV.C (17 pages)

- 410-254P-KIT (17 pages)

- 410-280P-KIT (9 pages)

- 410-202P-KIT (20 pages)

- 410-273P-KIT (24 pages)

- 410-269P-KIT (11 pages)

- 410-216P-KIT (15 pages)

- 410-231P-KIT (4 pages)

- 410-211P-KIT (10 pages)

- 410-262P-KIT (8 pages)

- 410-229P (7 pages)

- 410-242P-KIT (4 pages)

- 6021-210-000P-KIT (27 pages)

- 410-185P-KIT (21 pages)

- 6032-410-000P-BOARD (4 pages)

- 410-174P (17 pages)

- 410-145P (6 pages)

- 210-264P-BOARD (3 pages)

- 6003-210-012P (27 pages)

- 410-236P-BOARD (2 pages)

- 410-163P (1 page)

- 410-097P-KIT (2 pages)

- 410-255P-KIT (1 page)